# UNIVERSITÀ DEGLI STUDI DI ROMA "TOR VERGATA"

### Facoltà di Ingegneria

Tesi di Laurea Specialistica in Ingegneria Elettronica

# Analisi e progettazione di un decoder Digital Radio Mondiale basato su VLIW DSP

Laureando: Stefano Fasciani

Relatore: Prof. Marco Re Correlatore: Ing. Piergiovanni Bazzana

Anno Accademico 2004-2005

<u>Indice</u>

# **INDICE**

| INTROD   | UZIONE                                             | 10 |

|----------|----------------------------------------------------|----|

| CAPITOI  | LO 1                                               | 13 |

| IL DIGIT | AL AUDIO BROADCASTING (DAB)                        | 13 |

| 1.1      | PANORAMICA ATTUALE SUI SISTEMI DAB                 | 13 |

| 1.1.1    | Eureka 147                                         | 15 |

| 1.1.2    | ? iBiquity Digital's IBOC                          | 16 |

| 1.1.3    | 3 ISDB-T                                           | 18 |

| 1.1.4    | Satellite Digital Audio Radio Services             | 19 |

| 1.1.5    | 5 WorldSpace                                       | 20 |

| 1.1.6    | 6 Digital Radio Mondiale                           | 21 |

| 1.2      | VANTAGGI DEI SISTEMI DAB                           | 22 |

| 1.3      | RETI SFN                                           | 23 |

| 1.4      | LA MODULAZIONE OFDM                                | 25 |

| CAPITOI  | LO 2                                               | 29 |

| DRM: DI  | GITAL RADIO MONDIALE                               | 29 |

| 2.1      | IL CONSORZIO DRM                                   | 29 |

| 2.2      | ATTUALE UTILIZZO DELLA BANDA AM E BENEFICI DEL DRM | 36 |

| 2.2.1    | Allocazione delle frequenze in banda AM            | 42 |

| 2.2.2    | Propagazione delle ground-wave e delle sky-wave    | 42 |

| 2.3      | STANDARD ETSI ES 201 980 v2.2.1                    | 45 |

| 2.3.1    | La codifica di sorgente – MPEG-4                   | 46 |

| 2.3.2    | Struttura del DRM Multiplex                        | 50 |

| 2.3.3    | B Codifica di canale e modulazione                 | 53 |

| 2.3.4    | 4 Struttura trasmissiva                            | 66 |

| 2.3.5    | 5 Applicazioni multimediali del DRM                | 72 |

| CAPITOI  | LO 3                                               | 76 |

| RICEVIT  | ORI DRM                                            | 76 |

| 3.1      | RICEVITORI DRM PROFESSIONALI                       | 77 |

| 3.2      | RICEVITORI DRM STAND ALONE                         | 80 |

| 3.2.1    | Il modulo RadioScape RS500                         | 86 |

| 3.2.2    | 2 Il DSP TMS320DRM300/350                          | 90 |

| 3.3      | RICEZIONE DEL DRM MEDIANTE RICEVITORI HF           | 92 |

| 3.4      | RICEVITORI PC BASED                                | 94 |

| 3.5      | RICEVITORI DRM SOFTWARE                            | 99 |

| CAPITOL  | .0 4                                                               | 106  |

|----------|--------------------------------------------------------------------|------|

| ATMEL®   | DIOPSIS 740 DUAL-CORE DSP                                          | 106  |

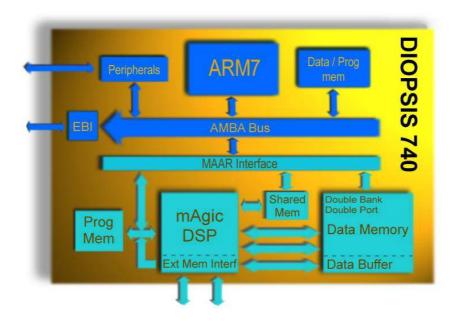

| 4.1      | CARATTERISTICHE TECNICHE                                           | 106  |

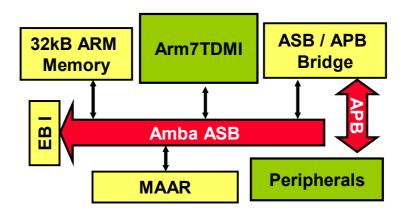

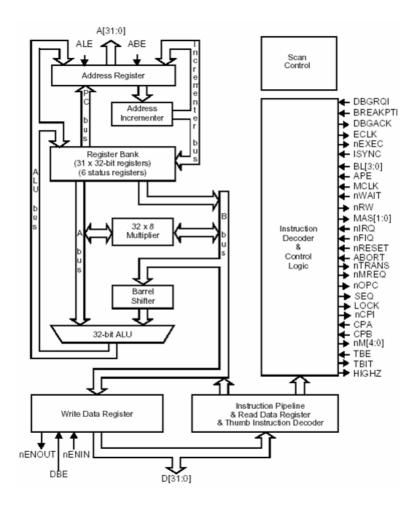

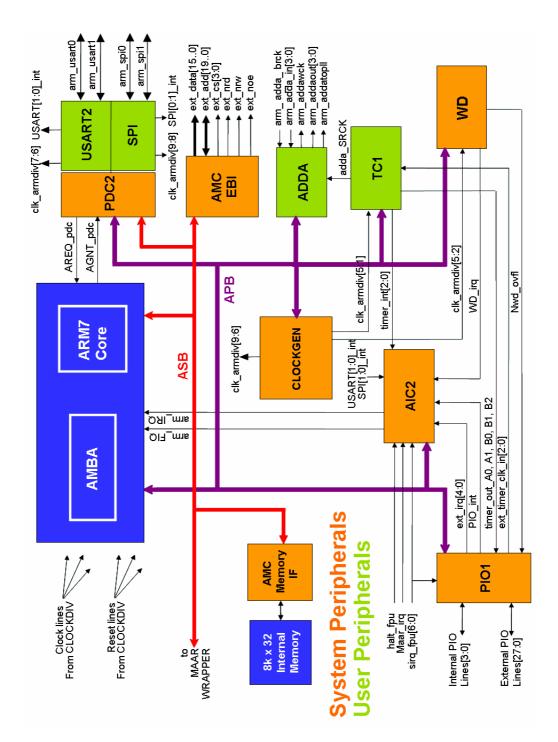

| 4.1.1    | ARM System                                                         | 109  |

| 4.1.2    | mAgic DSP processor                                                | 114  |

| 4.2      | TOOL DI SVILUPPO SOFTWARE                                          | 120  |

| 4.2.1    | MADE                                                               | 120  |

| 4.2.2    | Sistemi operativi eCos e mArmOS                                    | 122  |

| 4.2.3    | DSP Library                                                        | 125  |

| 4.3      | TOOL DI SVILUPPO HARDWARE                                          | 127  |

| 4.4      | PERFORMANCE A CONFRONTO CON ALTRI DSP                              | 130  |

| 4.5      | ATMEL® DIOPSIS 940 HF DUAL-CORE DSP                                | 133  |

| CAPITOL  | .0 5                                                               | 138  |

| ANALISI, | BREAKDOWN E PROFILING DEL RICEVITORE DRM                           | 138  |

| 5.1      | ALGORITMO DI DECODIFICA                                            | 140  |

| 5.1.1    | Demodulazione, sincronizzazione ed equalizzazione                  | 143  |

| 5.1.2    | Decodifica di canale                                               | 147  |

| 5.1.3    | Decodifica di sorgente                                             | 150  |

| 5.2      | Breakdown del ricevitore                                           | 150  |

| 5.2.1    | Breakdown ad alto livello                                          | 151  |

| 5.2.2    | Breakdown a basso livello                                          | 155  |

| 5.3      | PROFILING DELL'APPLICAZIONE                                        | 202  |

| CAPITOL  | .0 6                                                               | 206  |

| STUDIO I | DELL'IMPLEMENTAZIONE DEL RICEVITORE DRM SU DIOPSIS                 | 206  |

| 6.1      | INTERFACCIA ADC/DAC E DECODER MPEG-4 SU ARM                        | 207  |

| 6.2      | OTTIMIZZAZIONE E CALCOLO DELLA COMPLESSITÀ DEL PROCESSAMENTO IN BA | ANDA |

| BASE SU  | DSP MAGIC                                                          | 211  |

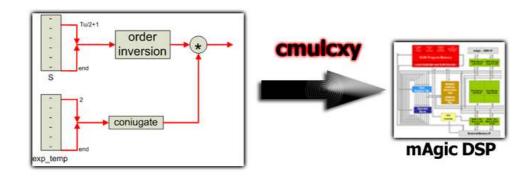

| 6.2.1    | Metodo di ottimizzazione                                           | 211  |

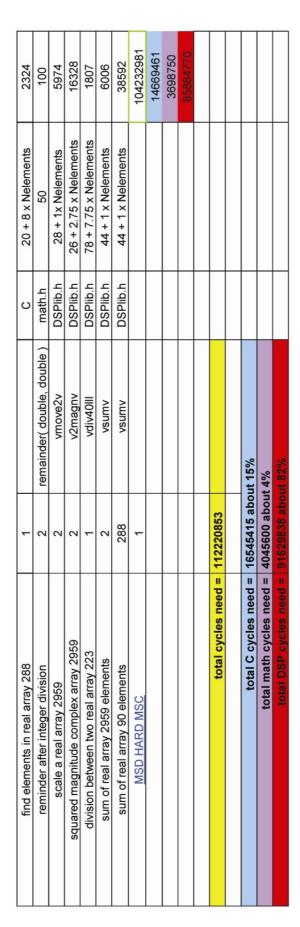

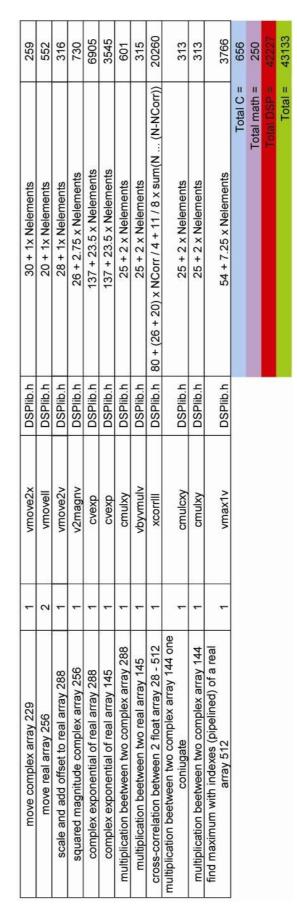

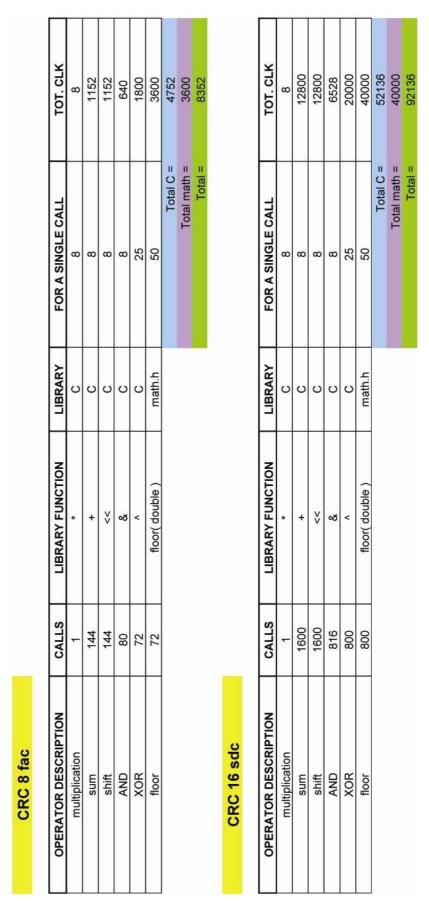

| 6.2.2    | Calcolo della complessità basata sui cicli di clock                | 214  |

| 6.2.3    | Valutazione dei risultati                                          | 230  |

| CAPITOL  | .0 7                                                               | 233  |

| CONCLU   | SIONI E SVILUPPI FUTURI                                            | 233  |

| 7.1      | CONTRIBUTO ORIGINALE                                               | 234  |

| 7.2      | SVILUPPI FUTURI                                                    | 235  |

| 7.3      | IL FUTURO DEL DRM                                                  | 236  |

| Refere   | NCES                                                               | 238  |

### **INDICE DELLE FIGURE**

| Figura 1: Confronto tra alcuni sistemi DAB                                   | 14 |

|------------------------------------------------------------------------------|----|

| Figura 2: Costo di distribuzione dei segnali DAB                             | 15 |

| Figura 3: iBiquity FM IBOC system                                            | 17 |

| Figura 4: iBiquity FM IBOC Hybrid system                                     | 18 |

| Figura 5: Copertura dei satelliti Worldspace                                 | 21 |

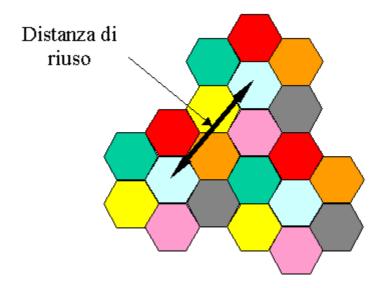

| Figura 6: Cluster convenzionale a 7 celle                                    | 24 |

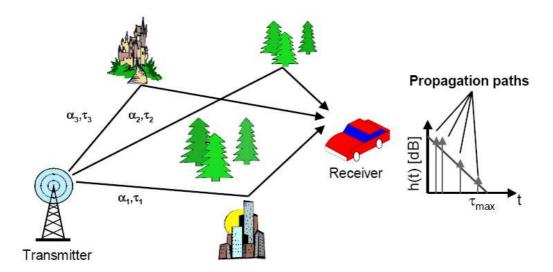

| Figura 7: Multi-Path propagation                                             | 26 |

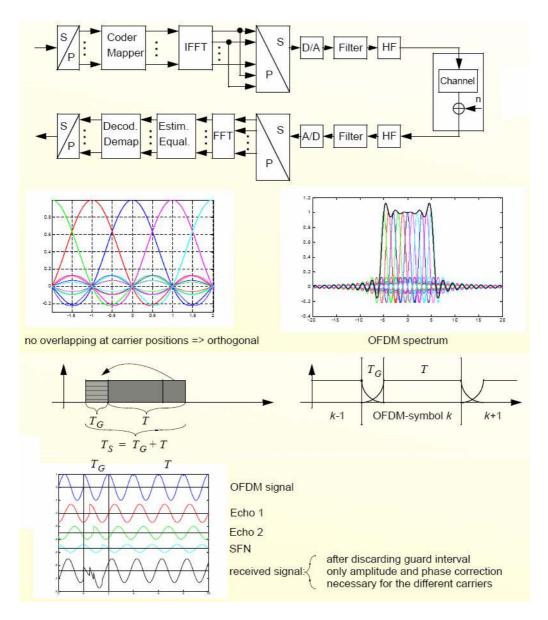

| Figura 8: The OFDM link functions                                            | 27 |

| Figura 9: Logo del consorzio DRM                                             | 31 |

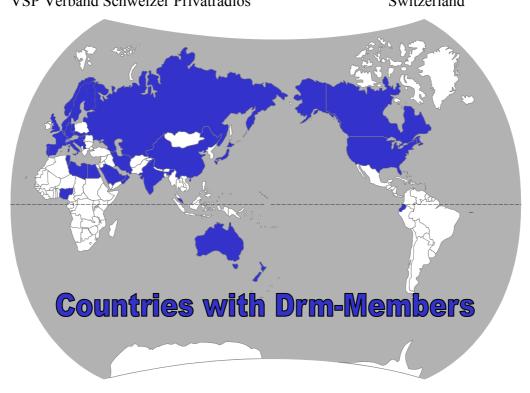

| Figura 10: Nazioni con membri DRM                                            | 35 |

| Figura 11: Uso delle attuali trasmittenti AM per il DRM                      | 39 |

| Figura 12: Propagazione delle ground-wave                                    | 43 |

| Figura 13: Propagazione delle sky-wave                                       | 44 |

| Figura 14: Propagazione NVIS                                                 | 45 |

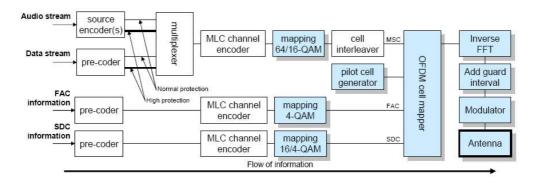

| Figura 15: Schema a blocchi di un trasmettitore DRM                          | 45 |

| Figura 16: MPEG-4 bit rates                                                  | 48 |

| Figura 17: DRM source encoder                                                | 48 |

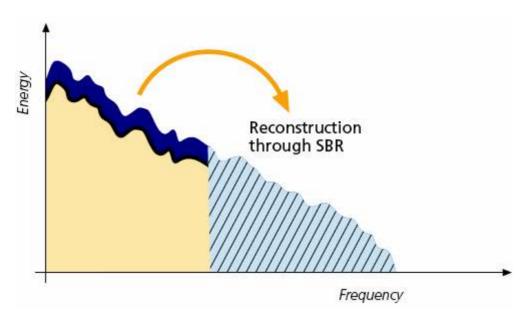

| Figura 18: Ricostruzione dello spettro mediante SBR                          | 49 |

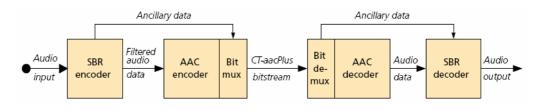

| Figura 19: Schema di principio dell'encoder e del decoder SBR + AAC          | 49 |

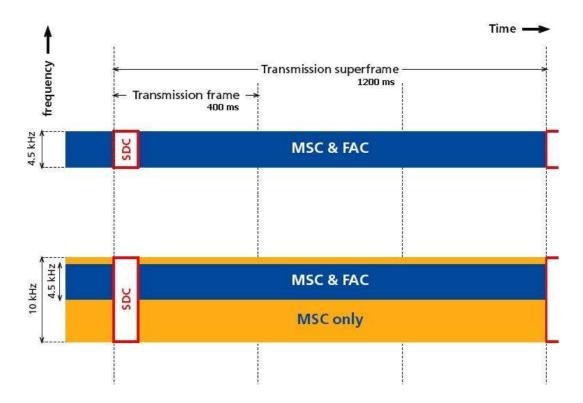

| Figura 20: Struttura del DRM Superframe                                      | 51 |

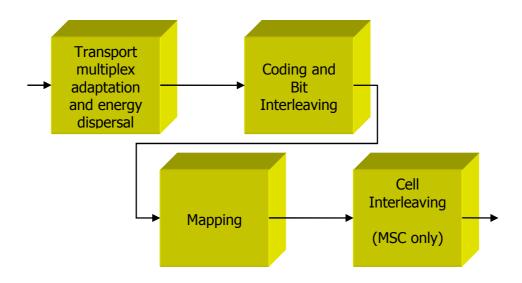

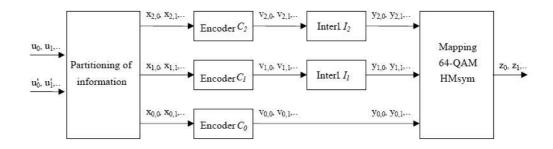

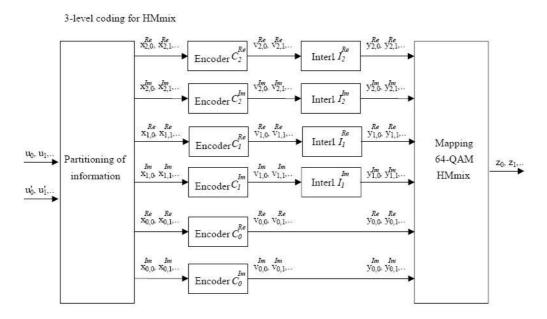

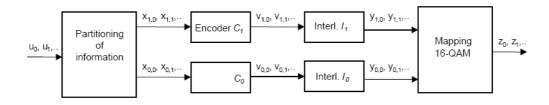

| Figura 21: Diagramma a blocchi funzionali della codifica e dell'interleaving | 53 |

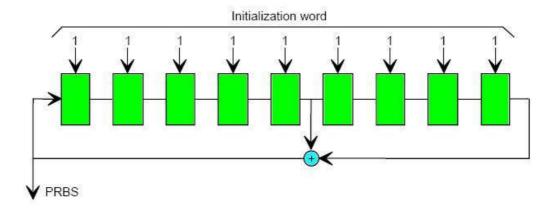

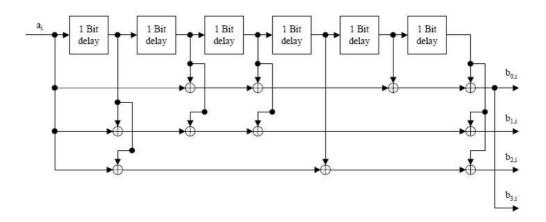

| Figura 22: Generatore PRBS                                                   | 55 |

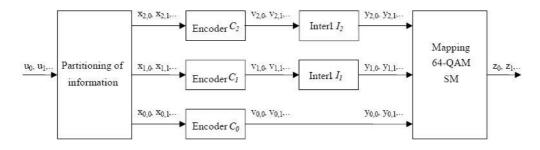

| Figura 23: Codifica multilivello a tre livelli per SM                        | 56 |

| Figura 24: Codifica multilivello a tre livelli per HMsym                     | 57 |

| Figura 25: Codifica multilivello a tre livelli per HMmix                     | 57 |

| Figura 26: Codifica multilivello a due livelli (SM )                         | 57 |

| Figura 27: Codifica multilivello ad un livello (SM)                          | 58 |

| Figura 28: Convolutional encoder                                             | 58 |

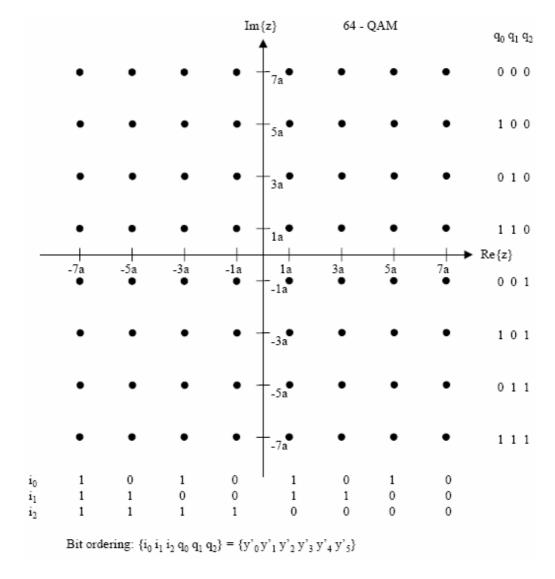

| Figura 29: SM 64-QAM mapping con il corrispondente bit pattern               | 60 |

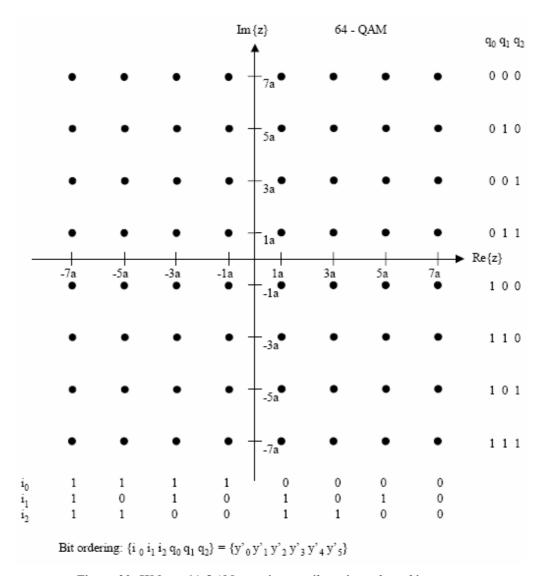

| Figura 30: HMsym 64-QAM mapping con il corrispondente bit pattern            | 61 |

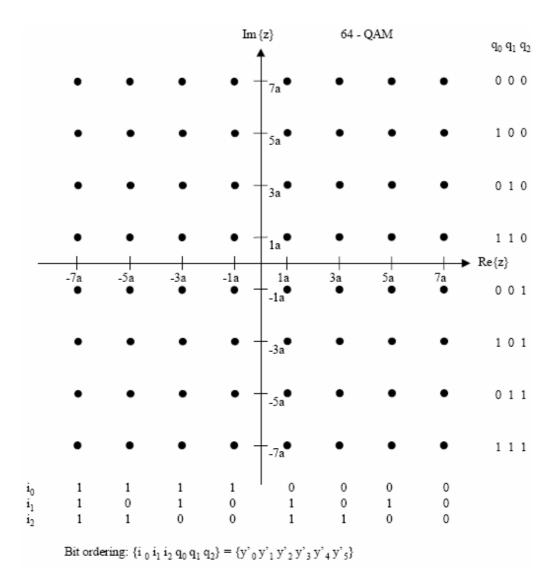

| Figura 31: HMmix 64-QAM mapping con il corrispondente bit pattern            | 62 |

| Figura 32: SM 16-QAM mapping con il corrispondente bit pattern               | 63 |

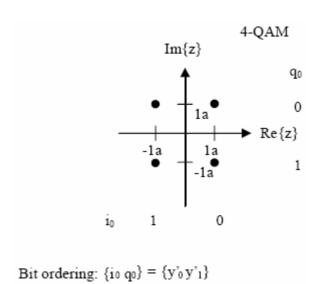

| Figura 33: SM 4-QAM mapping con il corrispondente bit pattern                | 63 |

| Figura 34: Dristibuzione dei simboli OFDM in frequenza e nel tempo           | 67 |

| Figura 35: Valori numerici dei parametri OFDM                                | 68 |

| Figura 36: Relazioni tra occupazione spettrale e larghezza di banda          | 68 |

| Figura 37: Occupazione spettrale per canali di 9 kHz                         |    |

| Figura 38: Occupazione spettrale per canali di 10 kHz                        | 69 |

| Figura 39: Indici delle portanti per ogni modo                           | 70  |

|--------------------------------------------------------------------------|-----|

| Figura 40: Portanti non utilizzate per ogni robustness mode              | 70  |

| Figura 41: Posizionamento nel tempo e nella frequenza del FAC e dell'SDC | 72  |

| Figura 42: Tabella riassuntiva modi DRM                                  | 74  |

| Figura 43: Tabella parametri OFDM nel DRM                                | 75  |

| Figura 44: Versione portatile del TSW 1002D                              | 78  |

| Figura 45: BBC R&D DRM receiver                                          | 79  |

| Figura 46: DRM monitoring receiver Telefunken                            | 80  |

| Figura 47: Prototype DRM consumer receiver e la scheda interna           | 81  |

| Figura 48: DRM receiver 2010                                             | 82  |

| Figura 49: Ricevitore Sangen RD-20                                       | 84  |

| Figura 50: Ricevitore Roberts RD-20                                      | 84  |

| Figura 51: Prototipo della Morphy Richards                               | 84  |

| Figura 52: Ricevitore Himalaya DRM2008                                   | 85  |

| Figura 53: Prototipi di car radio della Panasonic, Blaupunkt, Visteon    | 85  |

| Figura 54: Processore Blackfin Analog Devices                            | 86  |

| Figura 55: Il modulo RadioScape RS500                                    | 87  |

| Figura 56: Il RS500 montato su una scheda dimostrativa della RadioScape  | 87  |

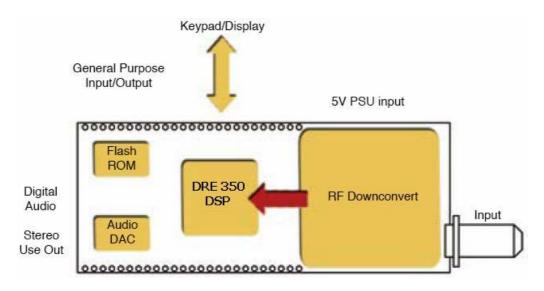

| Figura 57: Schema di principio dell'RS500                                | 89  |

| Figura 58: Caratteristiche tecniche dell'RS500                           | 89  |

| Figura 59: Caratteristiche RF dell'RS500                                 | 90  |

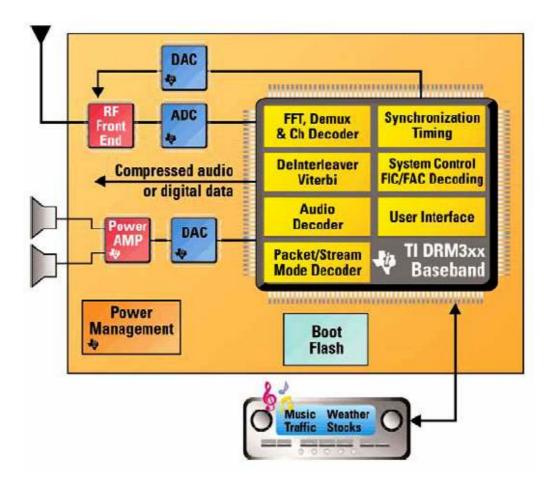

| Figura 60: Schema di un ricevitore DRM basato su TMS320DRM3xx            | 91  |

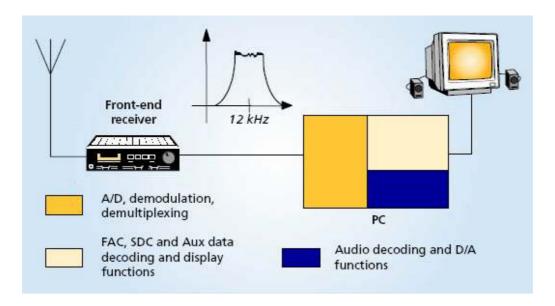

| Figura 61: Schema semplificato del funzionamento dei DRM SW receiver     | 92  |

| Figura 62: I diversi downconverter di Elad                               | 93  |

| Figura 63: Digital World Traveller Coding Technologies                   | 95  |

| Figura 64: Elad FDM77                                                    | 96  |

| Figura 65: Scheda PCD Winradio WRG303i                                   | 96  |

| Figura 66: Il modulo CIAOradio H101                                      | 97  |

| Figura 67: RFspace SDR14                                                 | 98  |

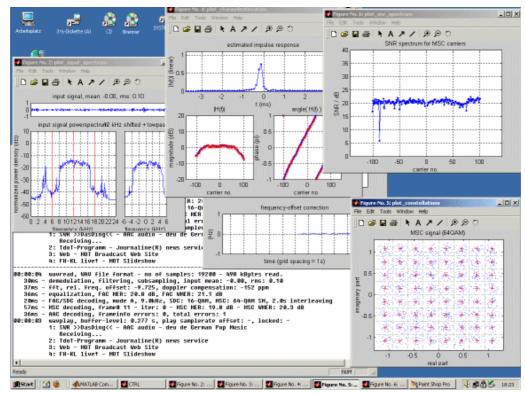

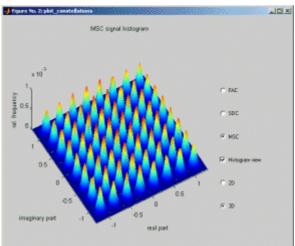

| Figura 68: Alcuni screenshot del SW DRM receiver DREAM                   | 101 |

| Figura 69: Schema a blocchi di DREAM                                     | 102 |

| Figura 70: Alcuni screenshot di DIORAMA                                  | 105 |

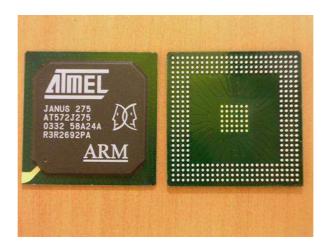

| Figura 71: ATMEL DIOPSISTM 740                                           | 107 |

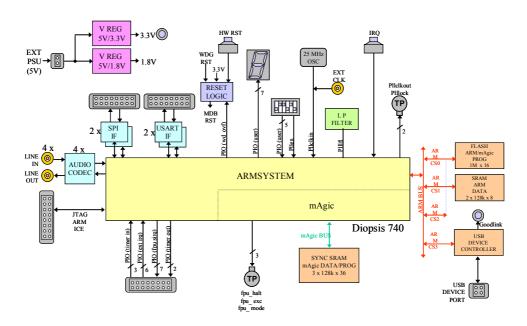

| Figura 72: Architettura interna del DIOPSIS <sup>TM</sup> 740            | 108 |

| Figura 73: Layout del Die del DIOPSIS <sup>TM</sup> 740                  | 108 |

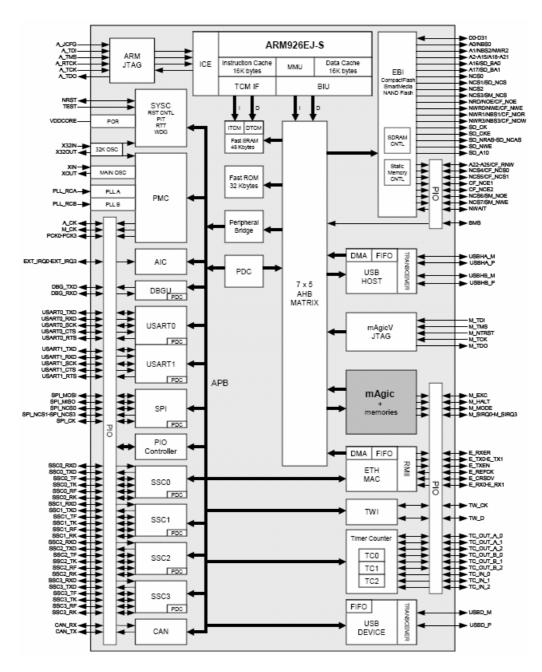

| Figura 74: Bus interni del sistema ARM                                   | 109 |

| Figura 75: Architettura del core di ARM                                  | 110 |

| Figura 76: Periferiche del sistema ARM                                   | 112 |

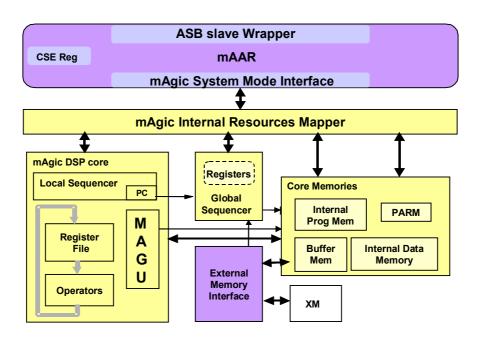

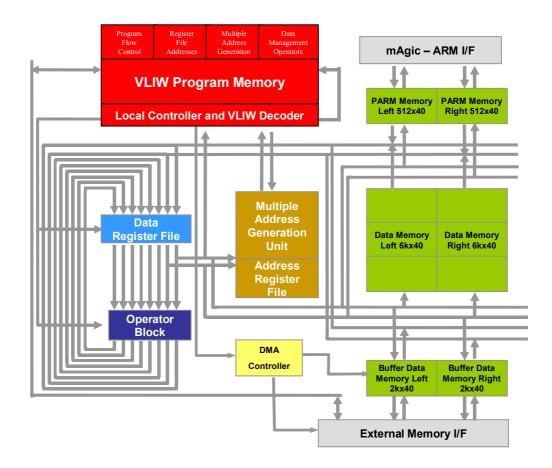

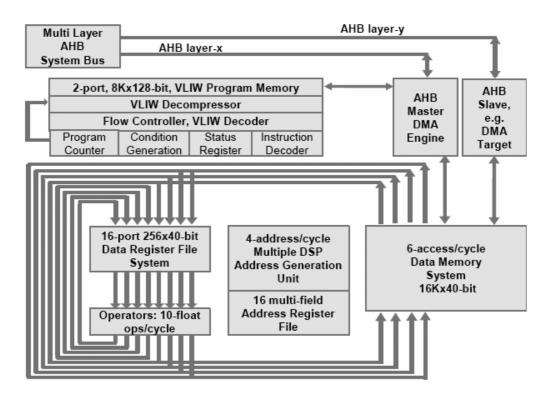

| Figura 77: Struttura interna del DSP mAgic                               | 115 |

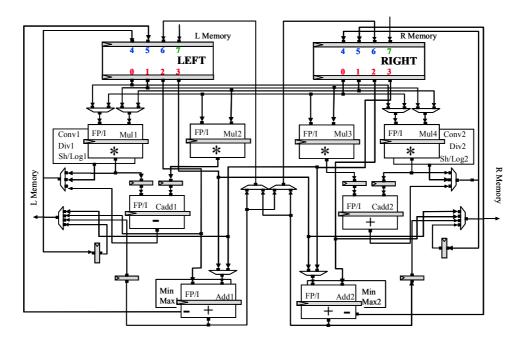

| Figura 78: Operatori interni di mAgic                                    | 116 |

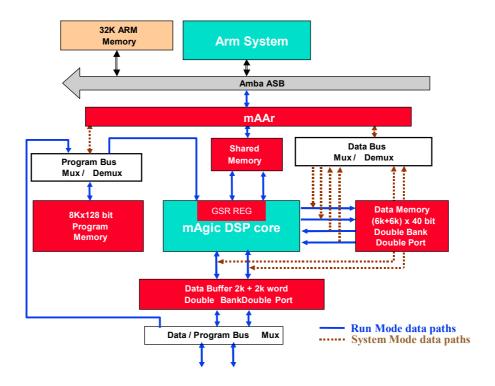

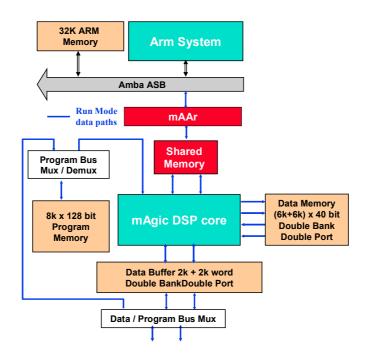

| Figura 79: mAgic in System Mode                                          | 118 |

|--------------------------------------------------------------------------|-----|

| Figura 80: mAgic in Run Mode                                             | 118 |

| Figura 81: Organizzazione della memoria in mAgic                         | 119 |

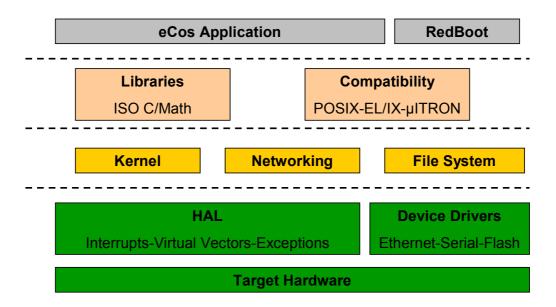

| Figura 82: Composizione delle istruzioni VLIW                            | 120 |

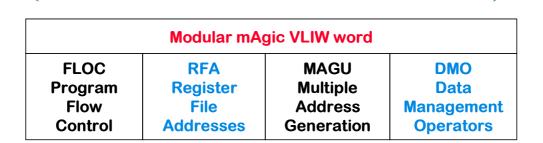

| Figura 83: Screenshot di MADE                                            | 121 |

| Figura 84: Flusso dello sviluppo di un applicazione utilizzando MADE     | 122 |

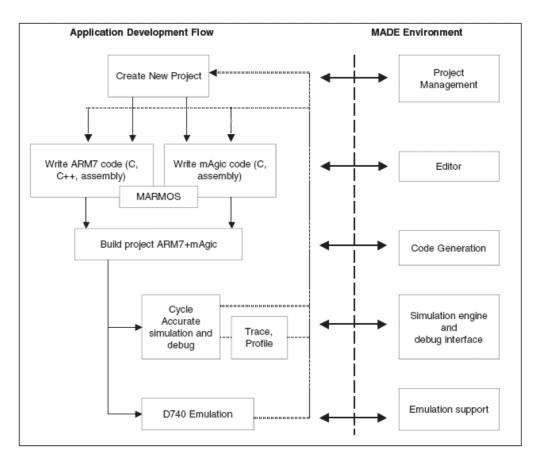

| Figura 85: Struttura di eCos                                             | 123 |

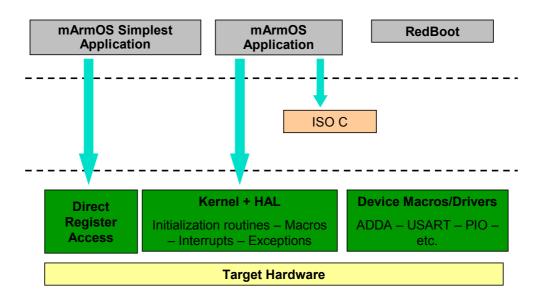

| Figura 86: Struttura di mArmOS                                           | 124 |

| Figura 87: eCos vs mArmOS                                                | 125 |

| Figura 88: Diagramma a blocchi della JTST                                | 128 |

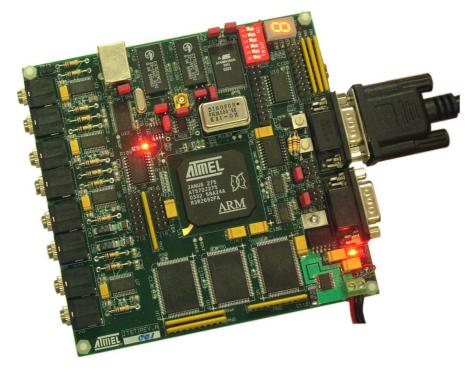

| Figura 89: ATMEL JTST con DIOPSIS740 on board                            | 128 |

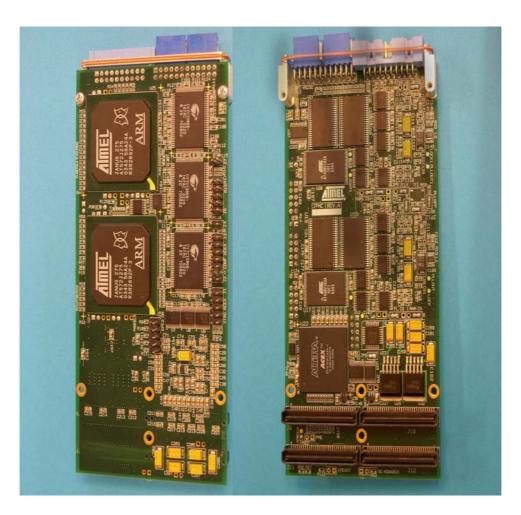

| Figura 90: ATMEL DJPMC                                                   | 129 |

| Figura 91: Risultati dei benchmark sui quattro DSP                       | 132 |

| Figura 92: DSP mAgic del DIOPSIS940 HF                                   | 134 |

| Figura 93: ATMEL DIOPSIS™ 940 HF                                         | 137 |

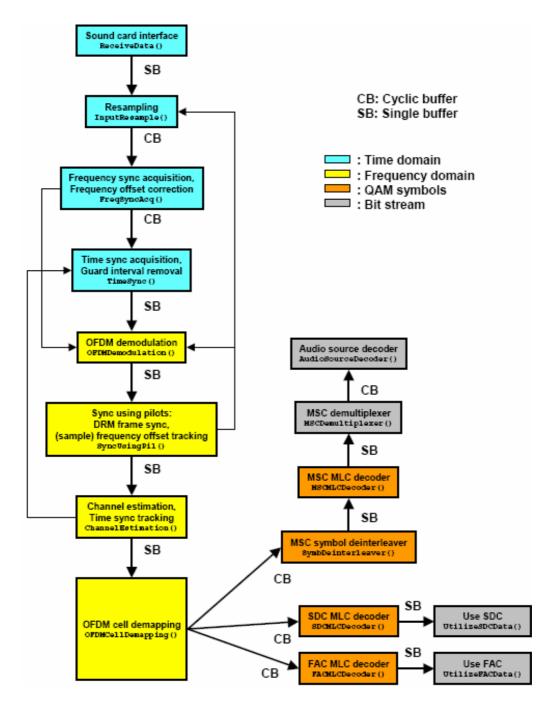

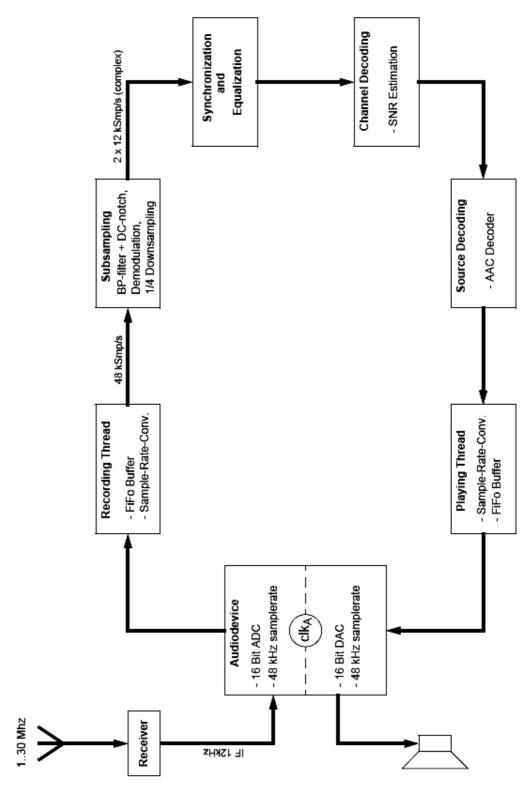

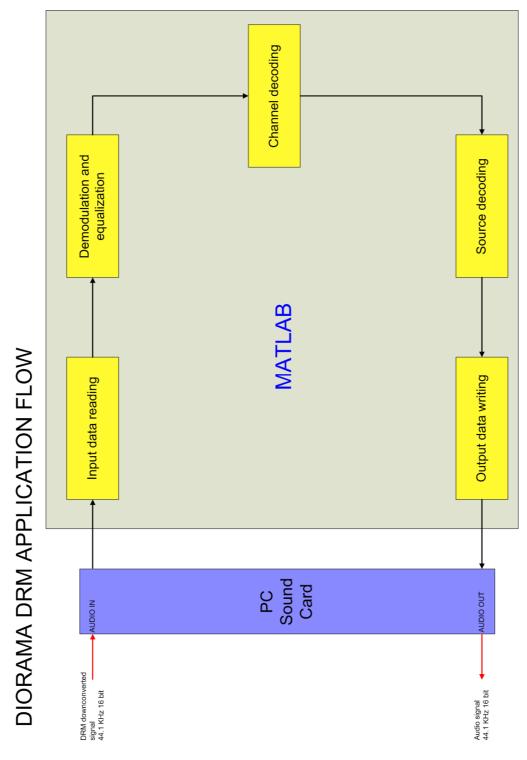

| Figura 94: Schema di principio di DIORAMA                                | 142 |

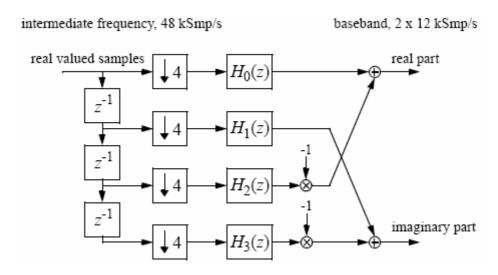

| Figura 95: Struttura polifase che demodula e sottocampiona               | 143 |

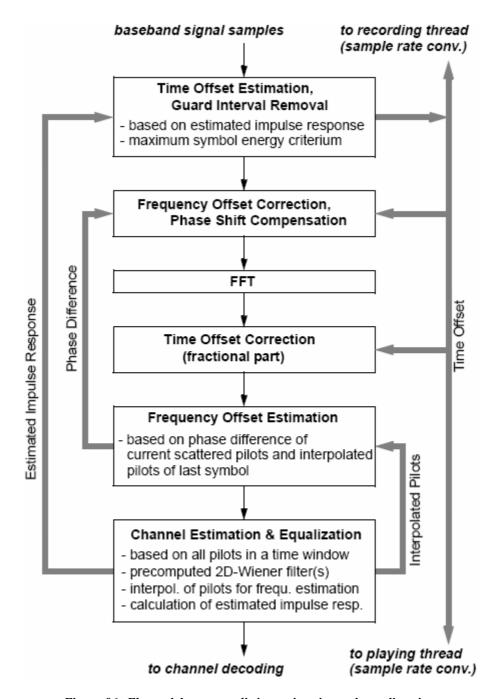

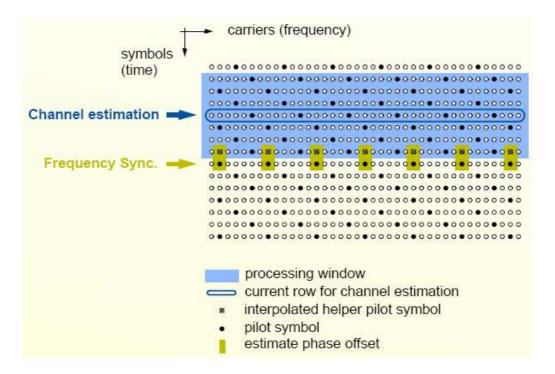

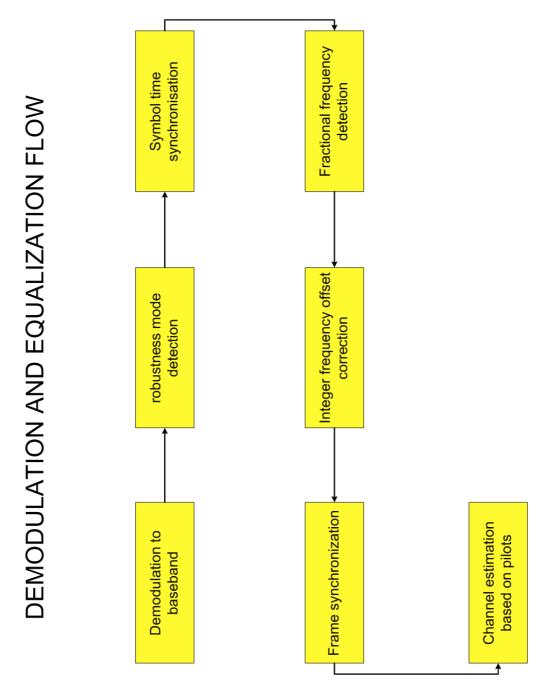

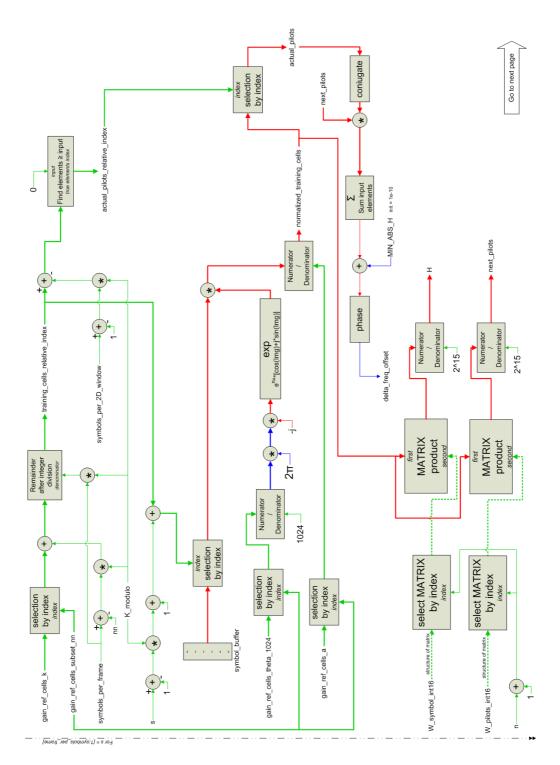

| Figura 96: Flusso del processo di sincronizzazione ed equalizzazione     | 144 |

| Figura 97: Filtraggio di Wiener bidimensionale                           | 145 |

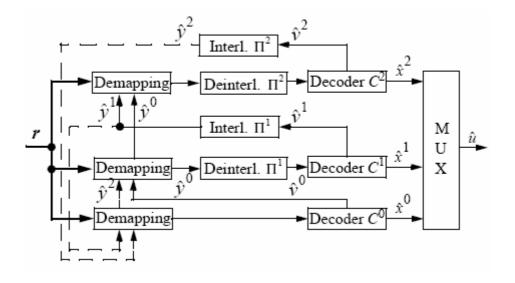

| Figura 98: Multi stage decoder per l'MSC                                 | 147 |

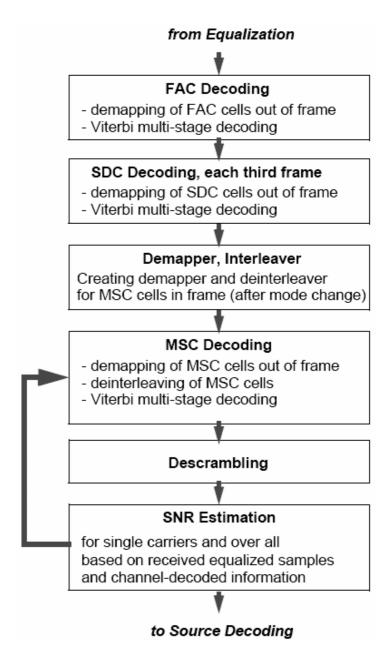

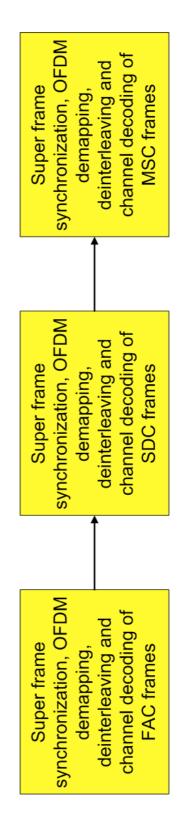

| Figura 99: Flusso del processo di decodifica di canale                   | 149 |

| Figura 100: Flusso delle 5 sottofunzioni di DIORAMA                      | 152 |

| Figura 101: Descrizione ad alto livello di demodulation and equalization | 153 |

| Figura 102: Descrizione ad alto livello di chennel decoding              | 154 |

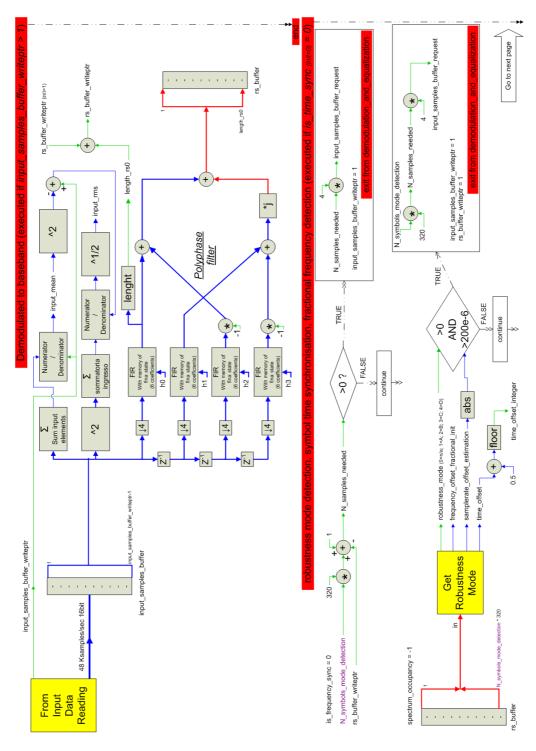

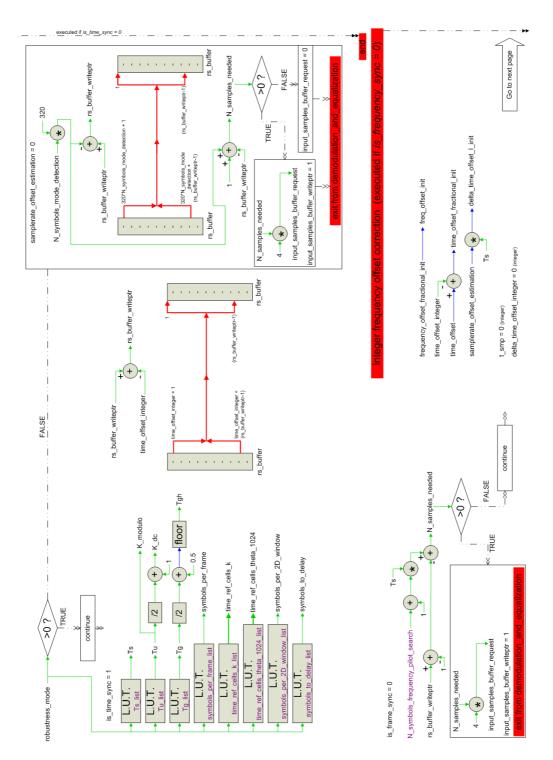

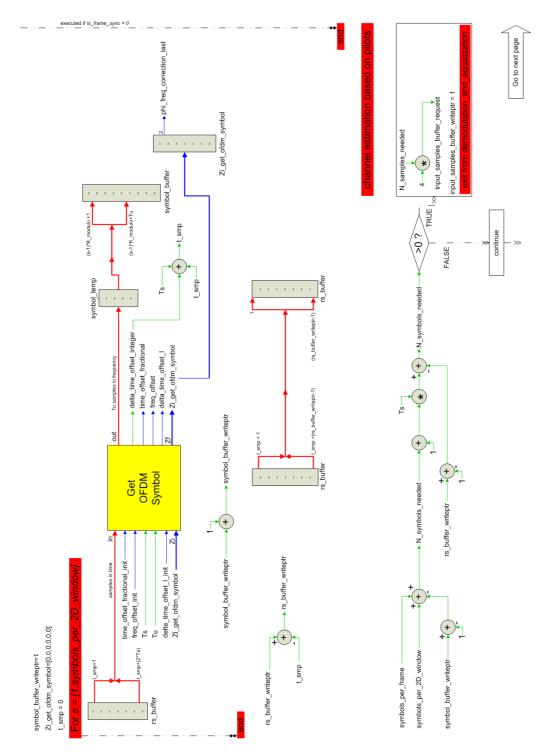

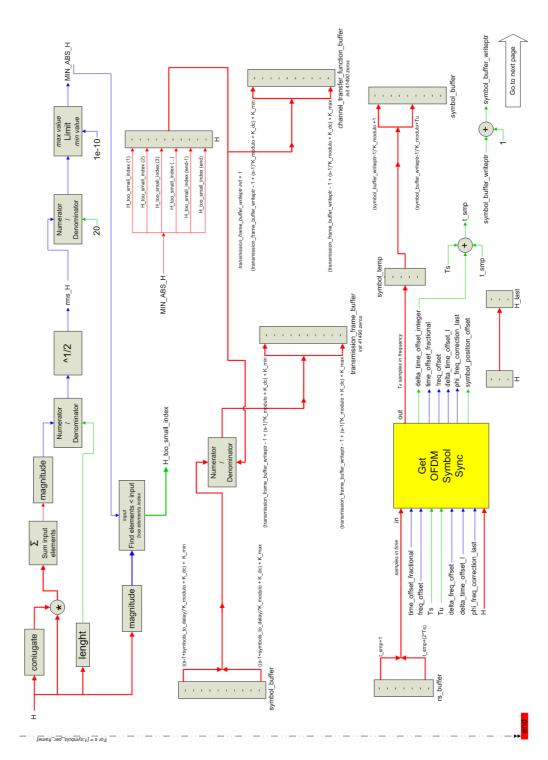

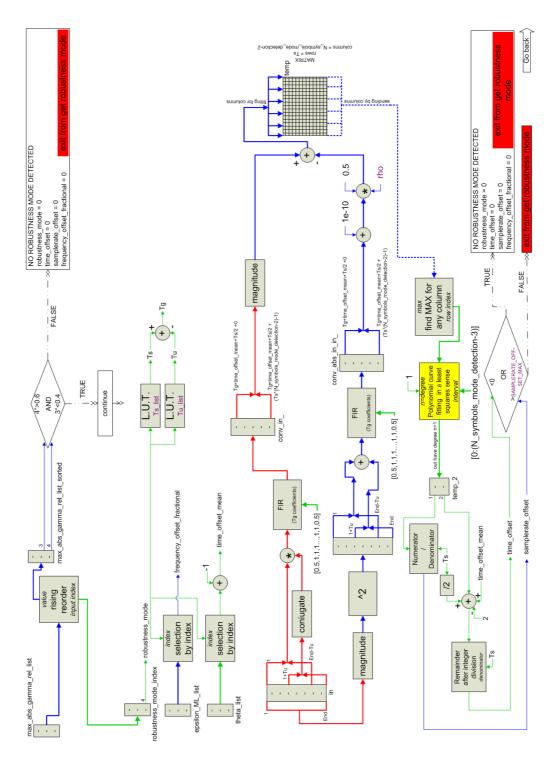

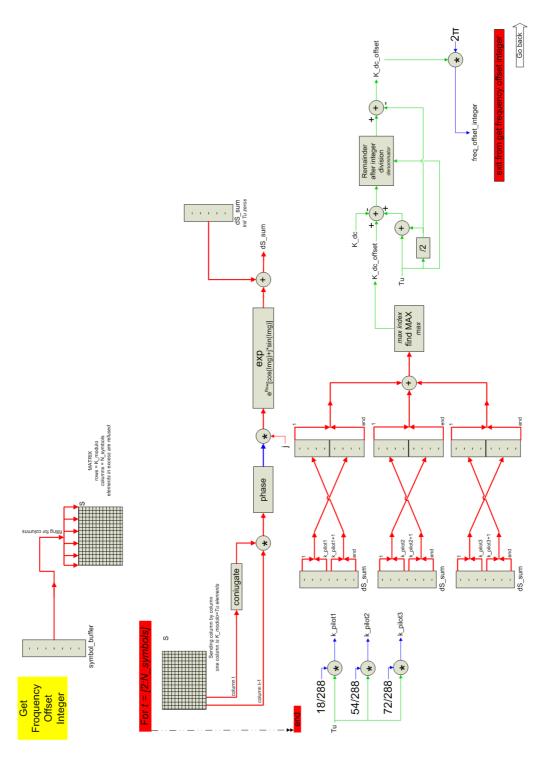

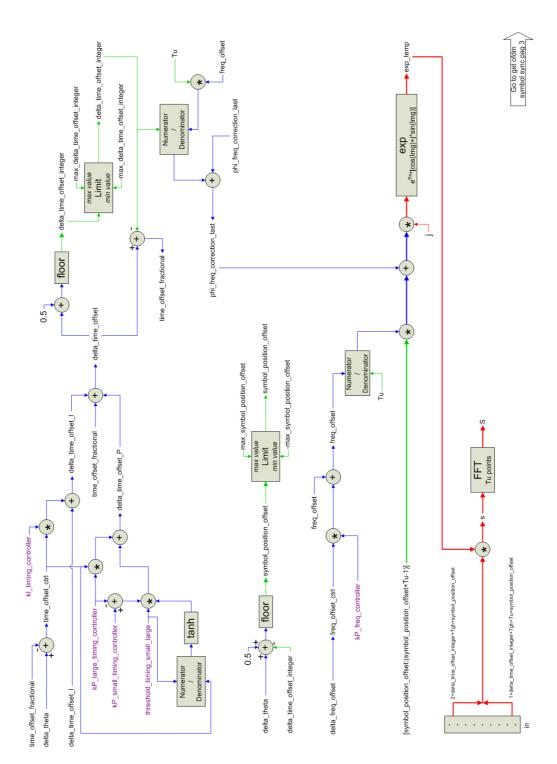

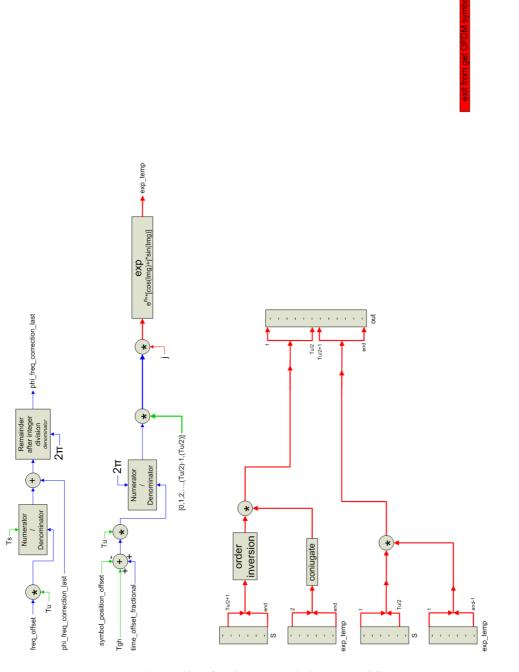

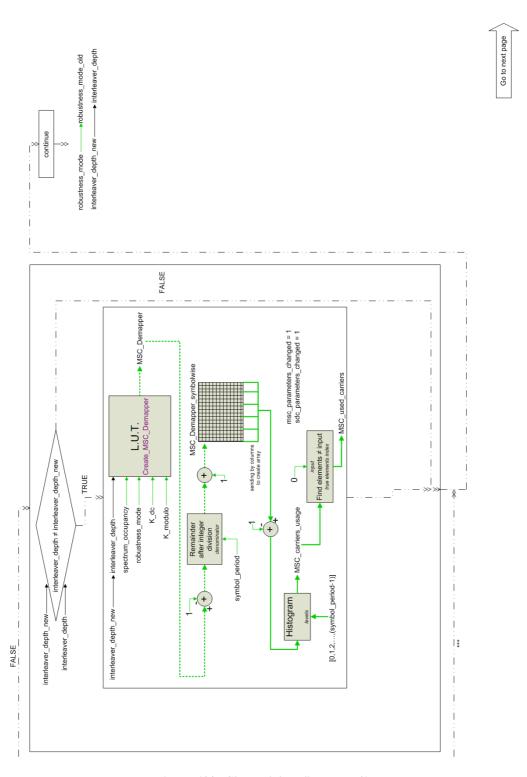

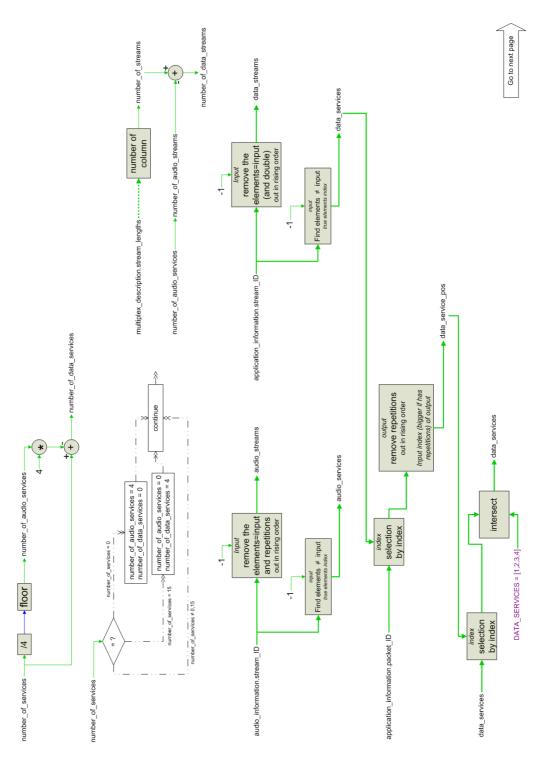

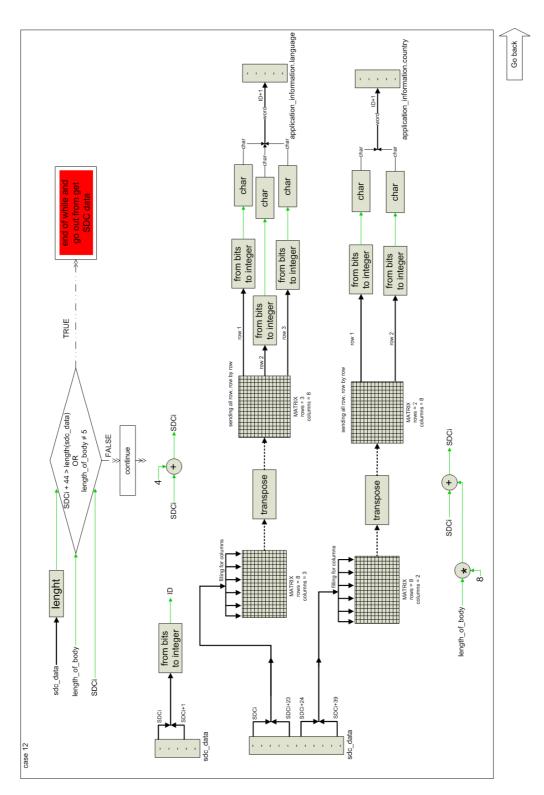

| Figura 103: Demodulation and equalization pag.1/12                       | 155 |

| Figura 104: Demodulation and equalization pag.2/12                       | 156 |

| Figura 105: Demodulation and equalization pag.3/12                       | 157 |

| Figura 106: Demodulation and equalization pag.4/12                       | 158 |

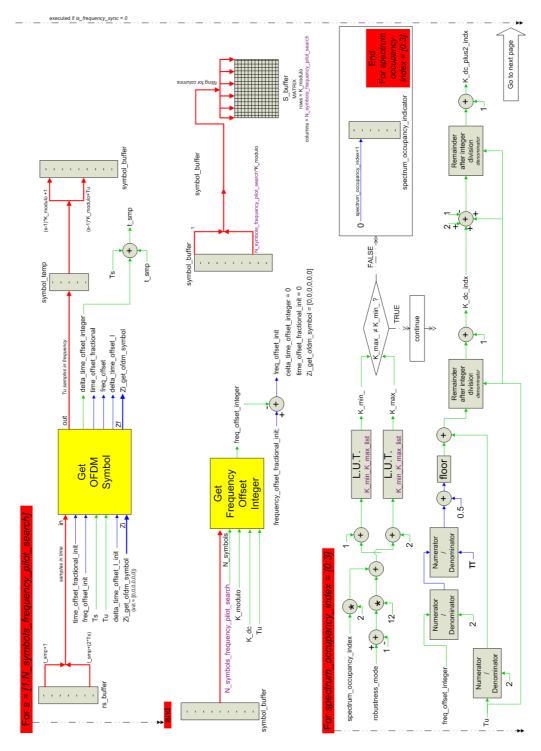

| Figura 107: Demodulation and equalization pag.5/12                       | 159 |

| Figura 108: Demodulation and equalization pag.6/12                       | 160 |

| Figura 109: Demodulation and equalization pag.7/12                       | 161 |

| Figura 110: Demodulation and equalization pag.8/12                       | 162 |

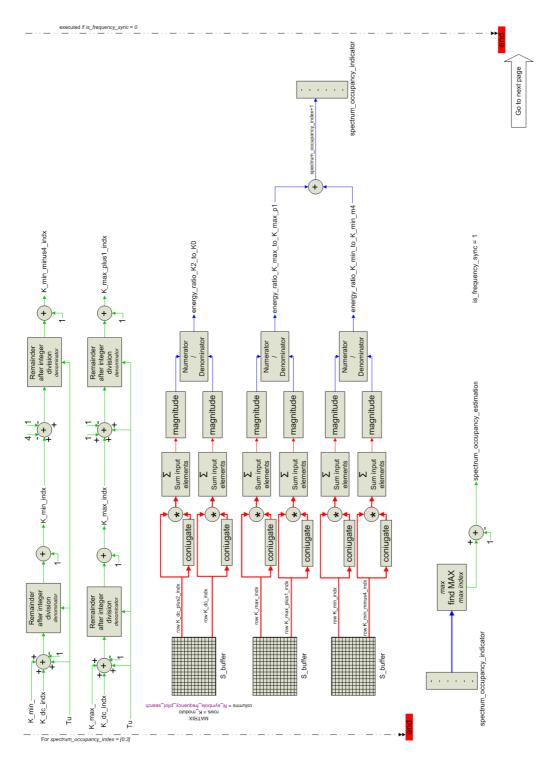

| Figura 111: Demodulation and equalization pag.9/12                       | 163 |

| Figura 112: Demodulation and equalization pag. 10/12                     | 164 |

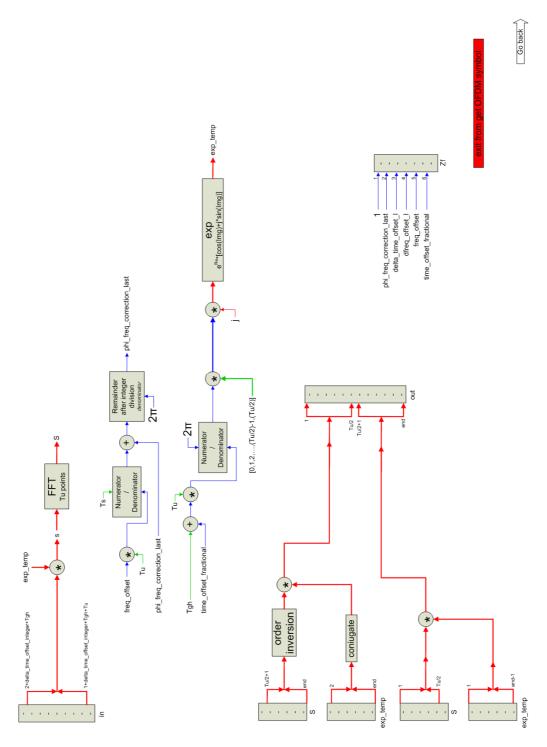

| Figura 113: Demodulation and equalization pag.11/12                      | 165 |

| Figura 114: Demodulation and equalization pag.12/12                      | 166 |

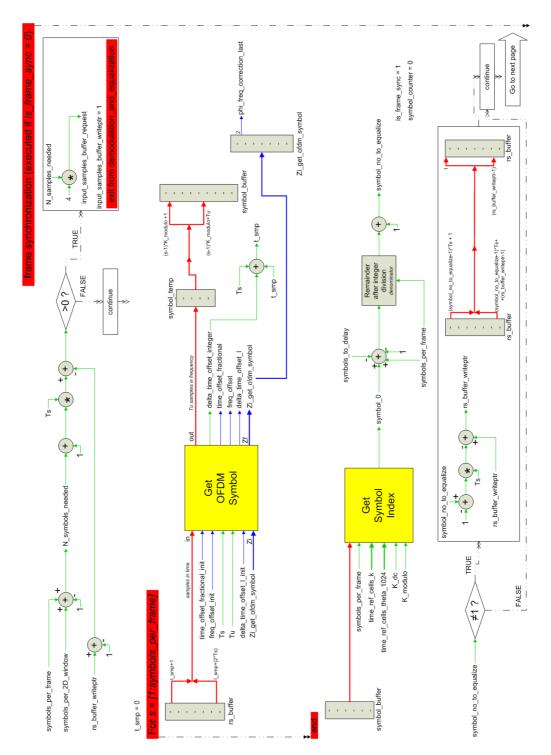

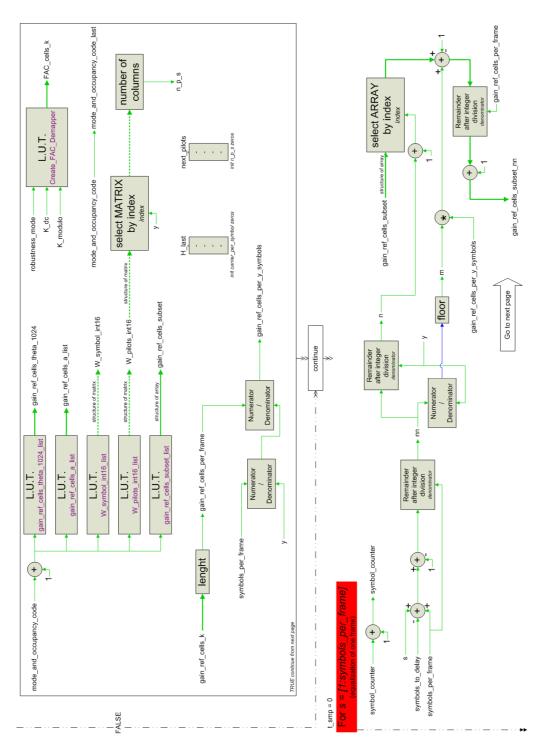

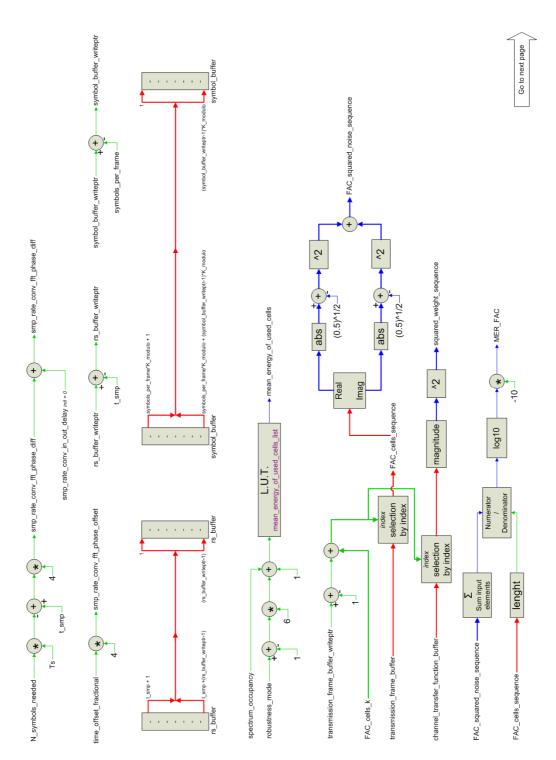

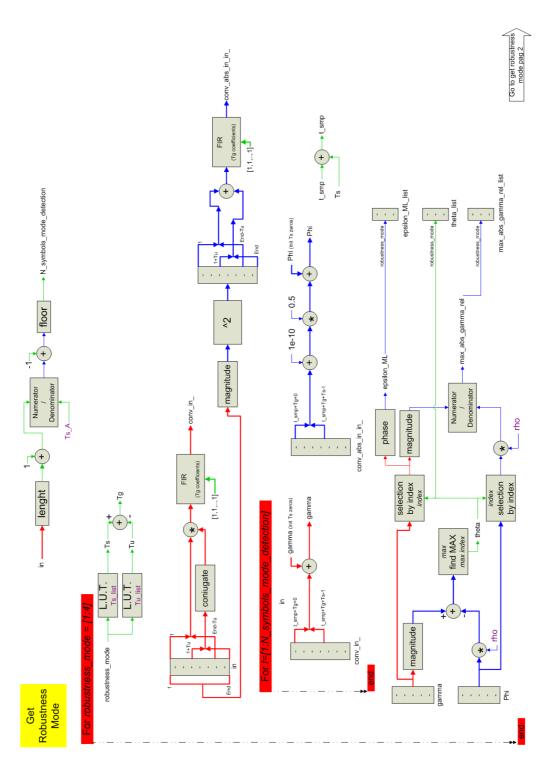

| Figura 115: Get robustness mode pag. 1/2                                 | 167 |

| Figura 116: Get robustness mode pag.2/2                                  | 168 |

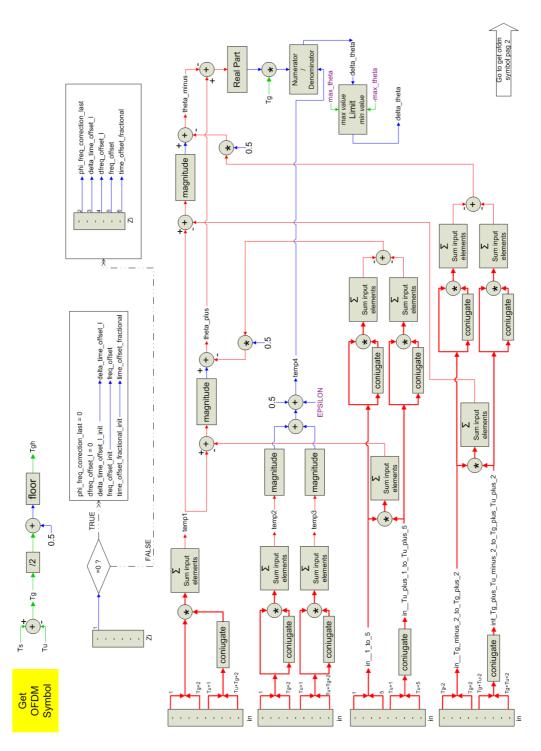

| Figura 117: Get ODFM symbol pag.1/3                                      | 169 |

| Figura 118: Get ODFM symbol pag.2/3                                      | 170 |

<u>Indice</u> 8

| Figura 119: Get ODFM symbol pag.3/3                          | 171 |

|--------------------------------------------------------------|-----|

| Figura 120: Get frequency offset integer                     | 172 |

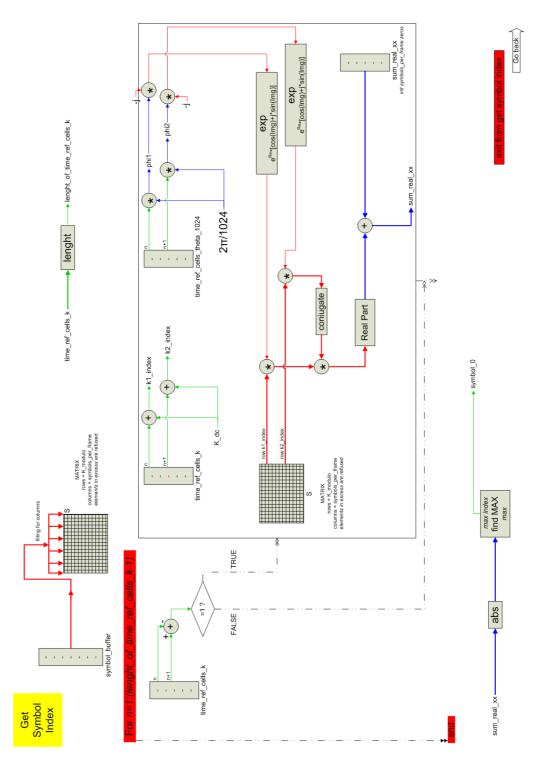

| Figura 121: Get symbol index                                 | 173 |

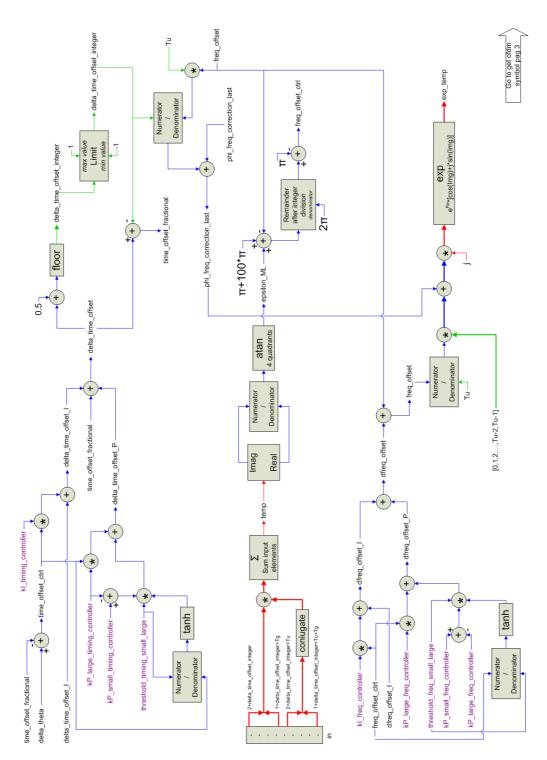

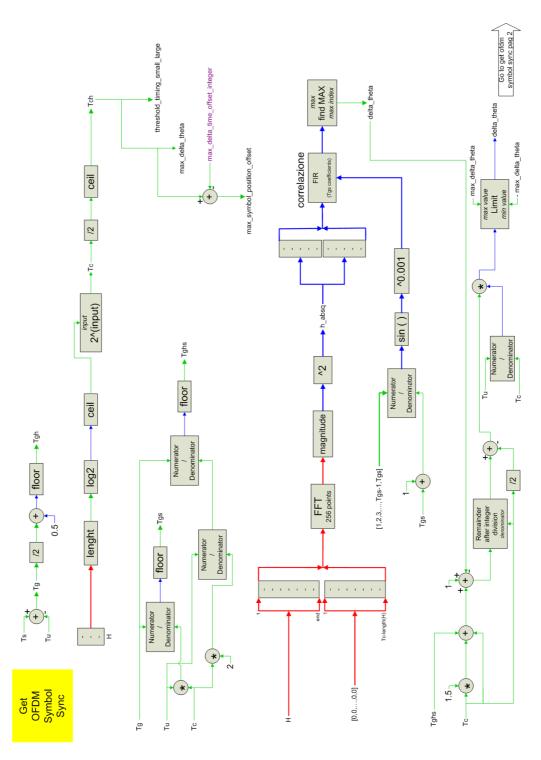

| Figura 122: Get OFDM symbol sync pag. 1/3                    | 174 |

| Figura 123: Get OFDM symbol sync pag. 2/3                    | 175 |

| Figura 124: Get OFDM symbol sync pag.3/3                     | 176 |

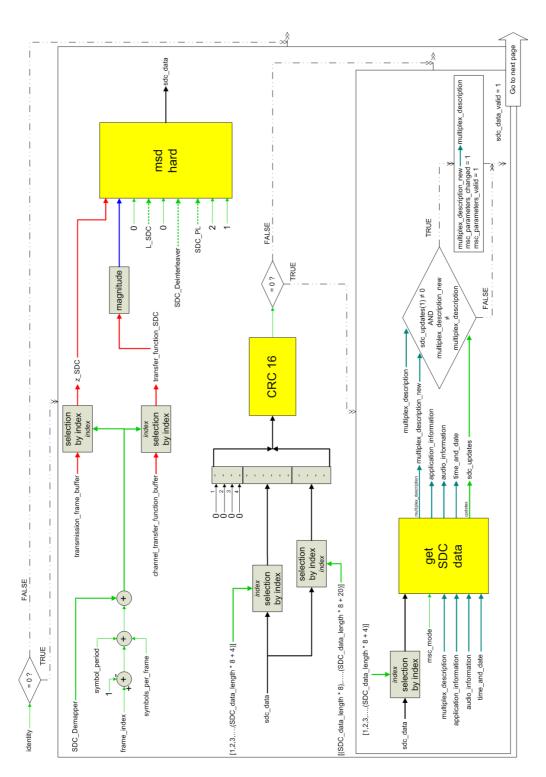

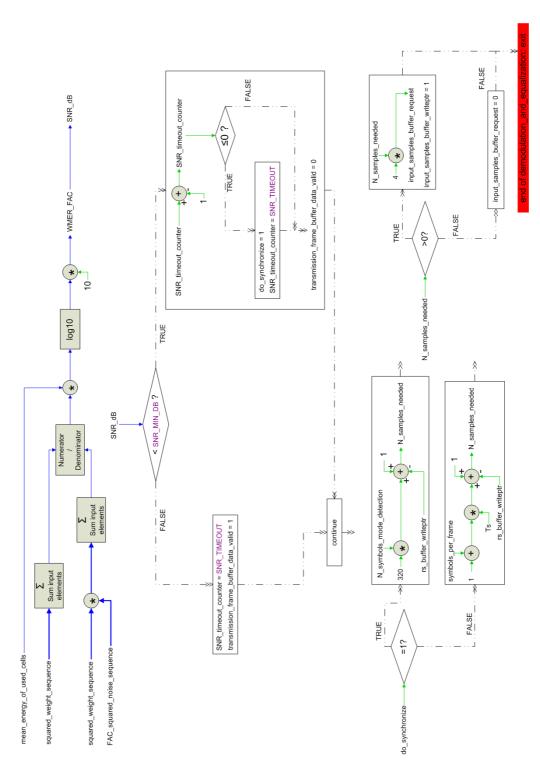

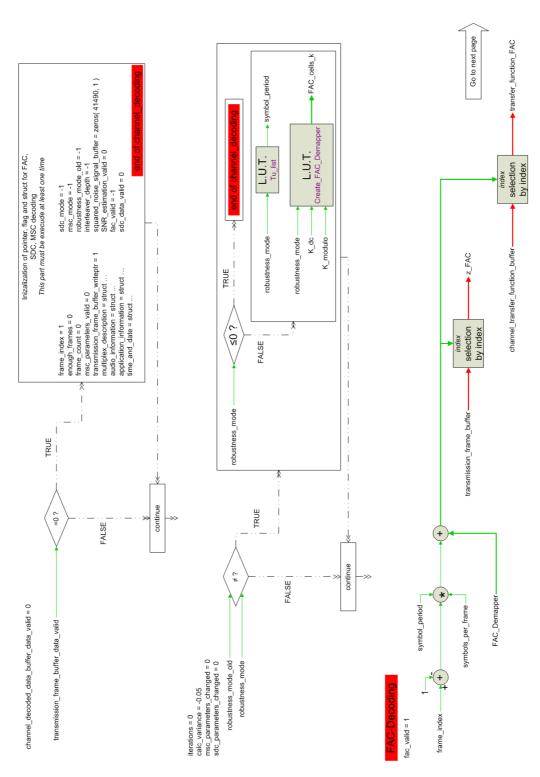

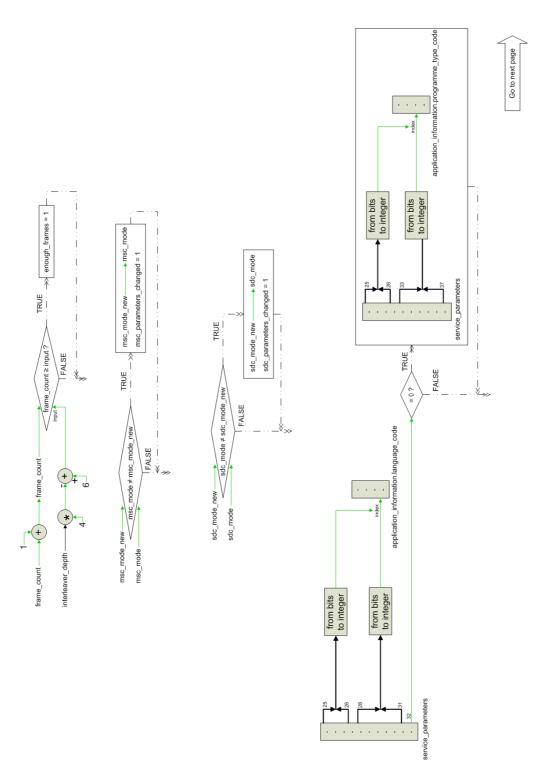

| Figura 125: Channel decoding pag.1/15                        | 177 |

| Figura 126: Channel decoding pag.2/15                        | 178 |

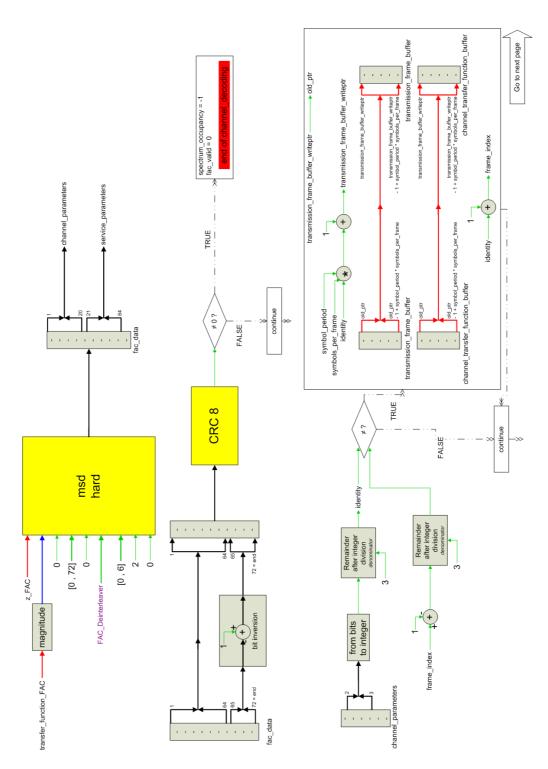

| Figura 127: Channel decoding pag.3/15                        | 179 |

| Figura 128: Channel decoding pag.4/15                        | 180 |

| Figura 129: Channel decoding pag.5/15                        | 181 |

| Figura 130: Channel decoding pag.6/15                        | 182 |

| Figura 131: Channel decoding pag.7/15                        | 183 |

| Figura 132: Channel decoding pag.8/15                        | 184 |

| Figura 133: Channel decoding pag.9/15                        | 185 |

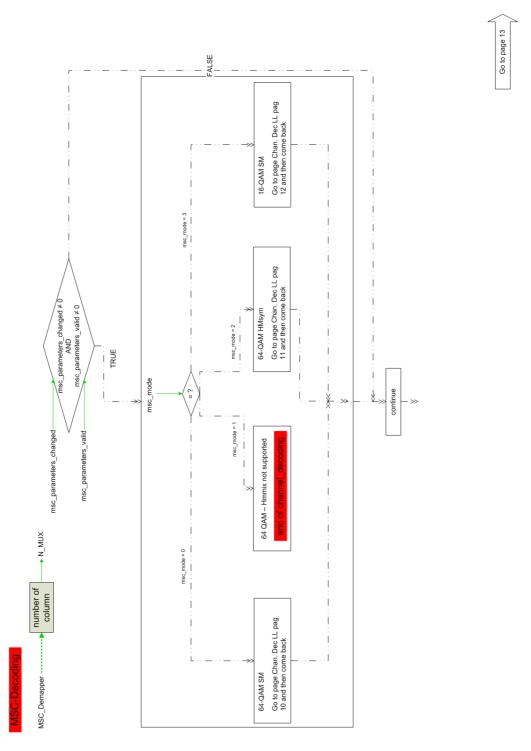

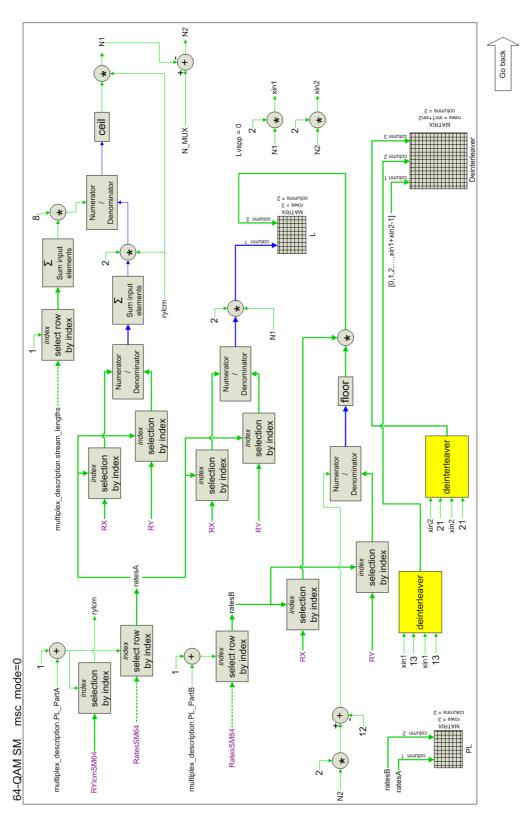

| Figura 134: Channel decoding - msc mode 0 - pag.10/15        | 186 |

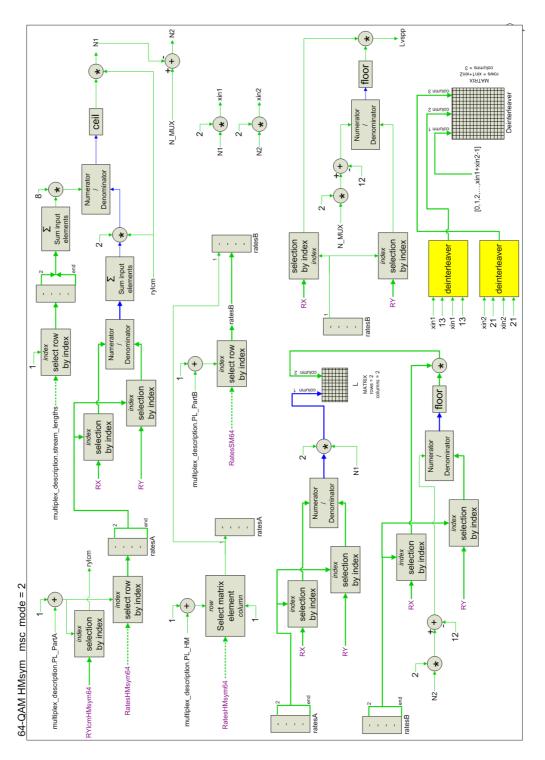

| Figura 135: Channel decoding - msc mode 2 - pag.11/15        | 187 |

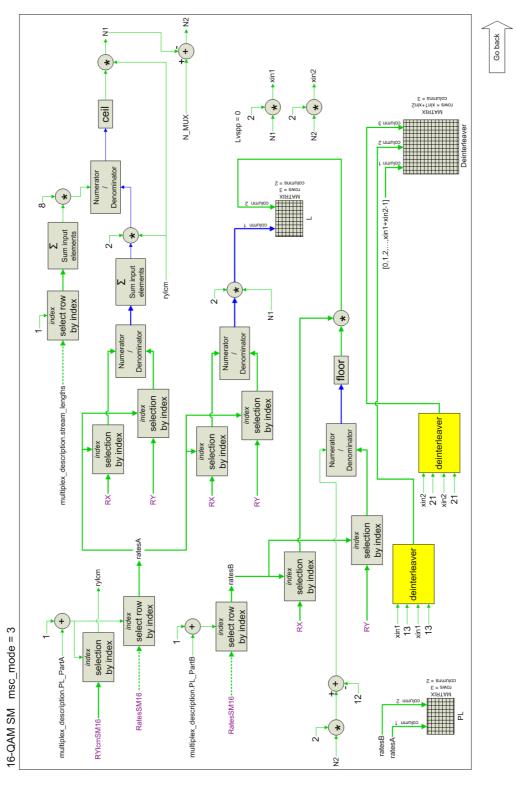

| Figura 136Channel decoding - msc mode 3 - pag.12/15          | 188 |

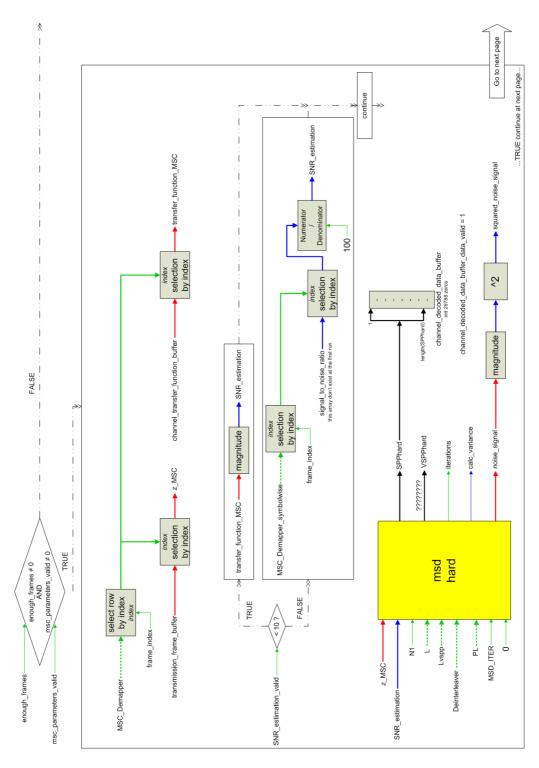

| Figura 137: Channel decoding pag.13/15                       | 189 |

| Figura 138: Channel decoding pag.14/15                       | 190 |

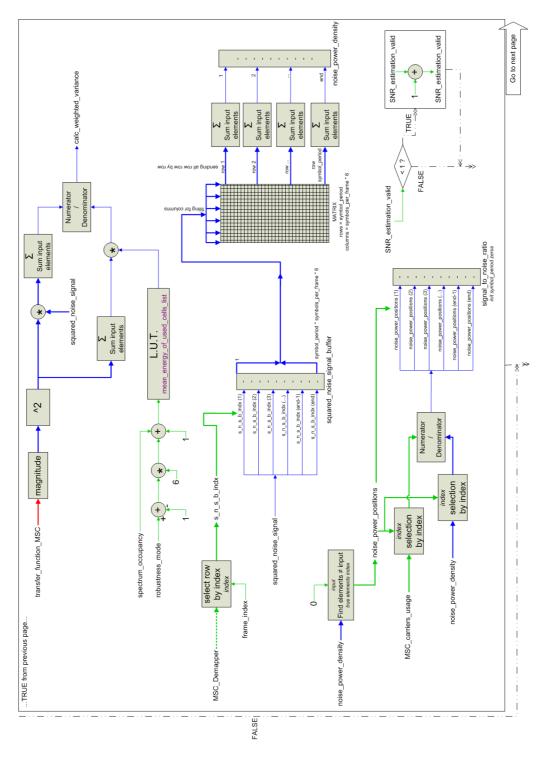

| Figura 139: Channel decoding pag.15/15                       | 191 |

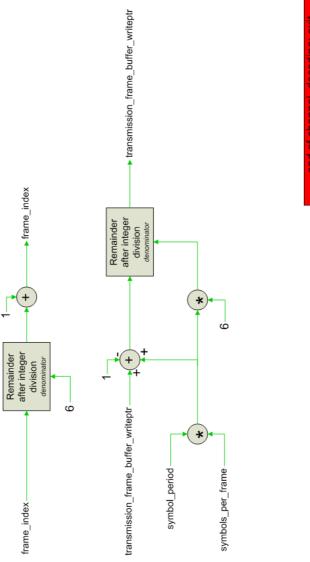

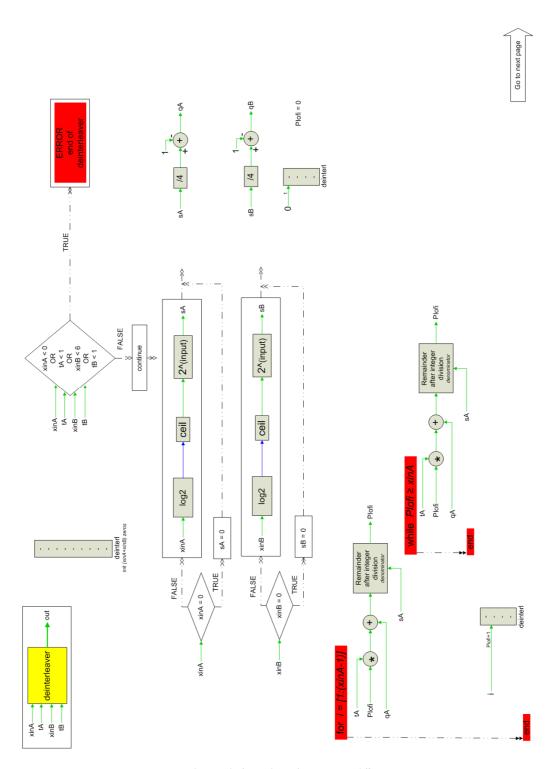

| Figura 140: Deinterleaver pag. 1/2                           | 192 |

| Figura 141:Deinterleaver pag.2/2                             | 193 |

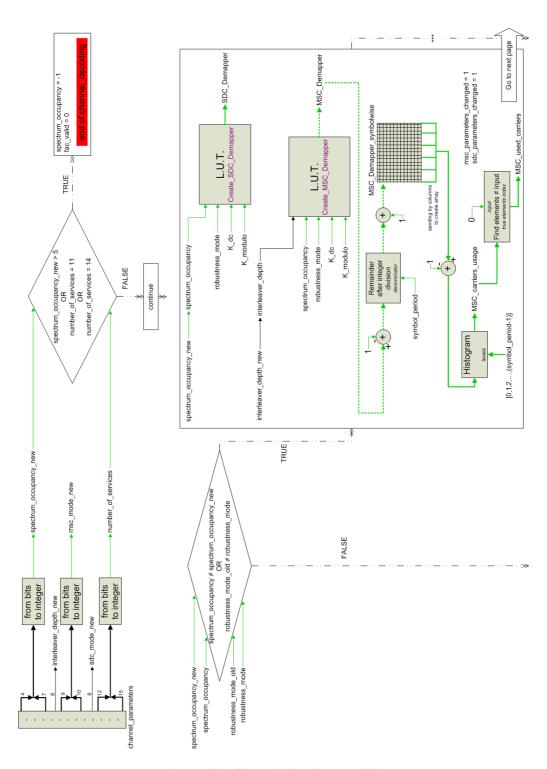

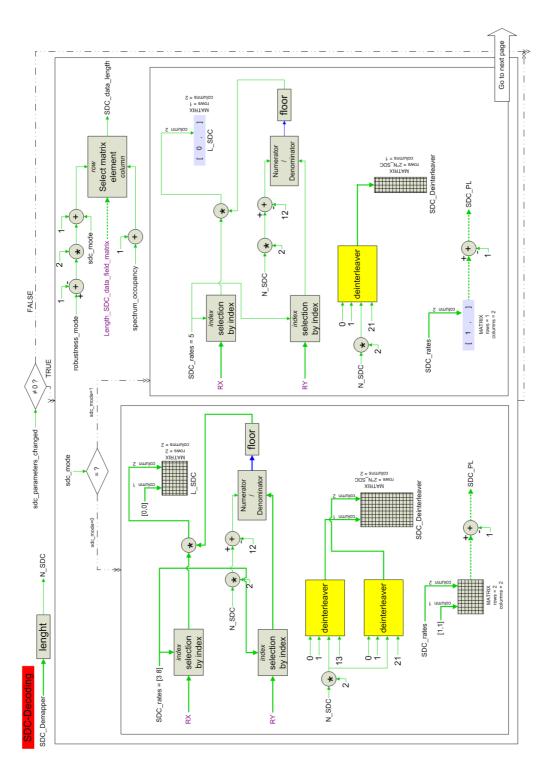

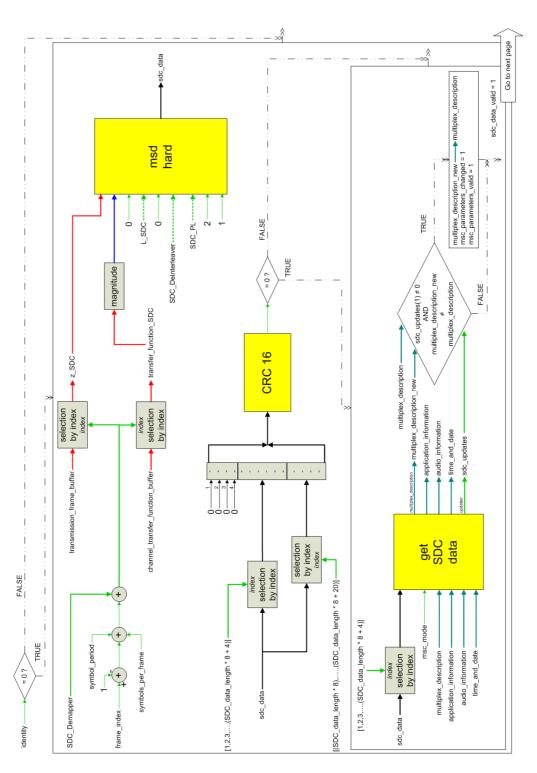

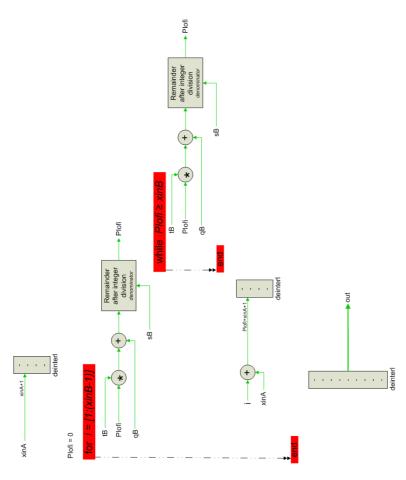

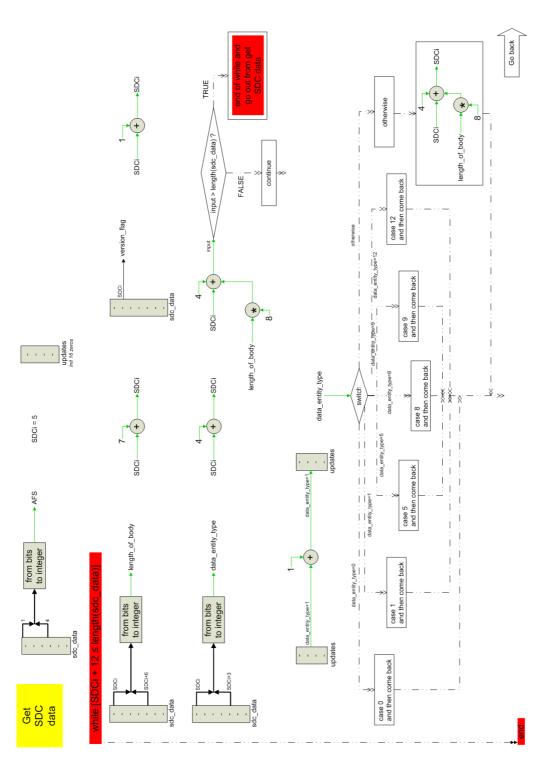

| Figura 142: Get SDC data pag.1/7                             | 194 |

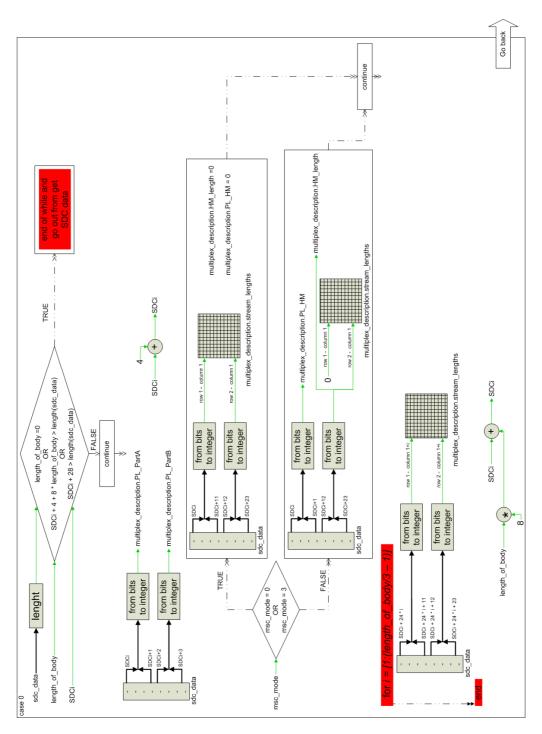

| Figura 143: Get SDC data – case 0 - pag.2/7                  | 195 |

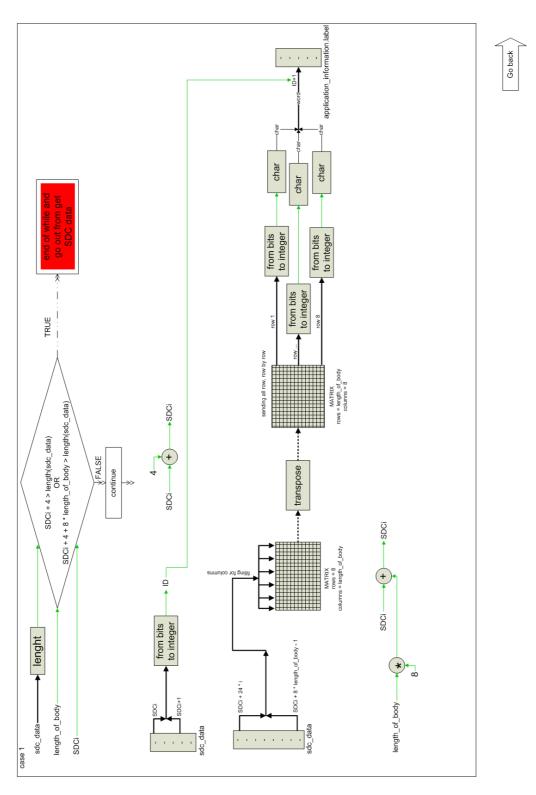

| Figura 144: Get SDC data - case 1 - pag.3/7                  | 196 |

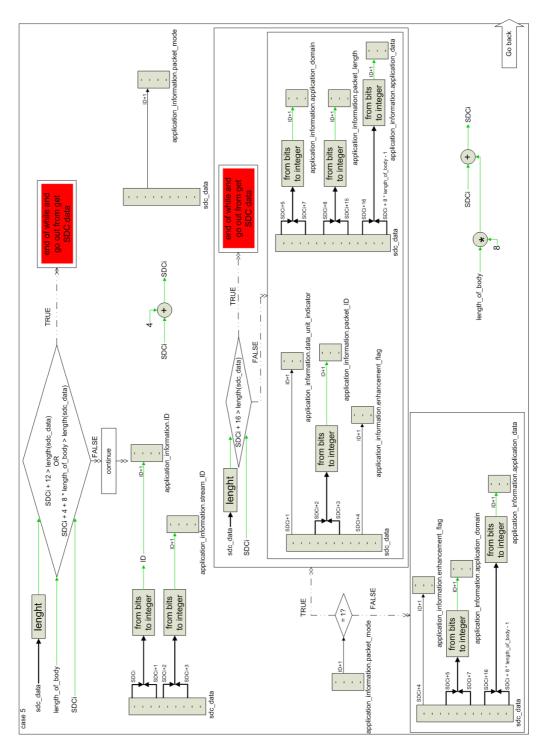

| Figura 145: Get SDC data - case 5 - pag.4/7                  | 197 |

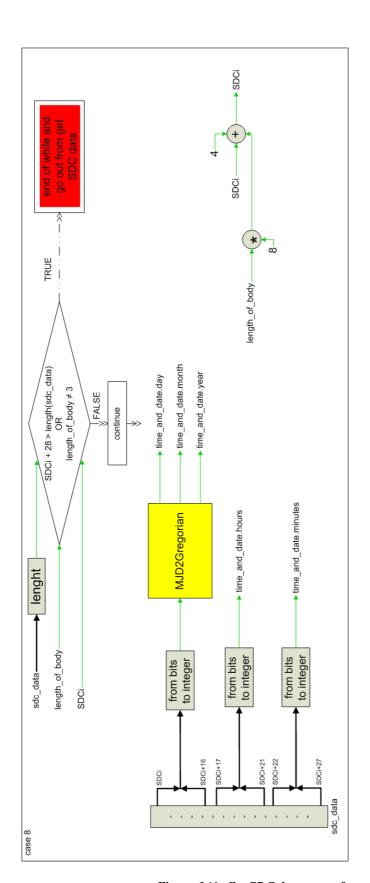

| Figura 146: Get SDC data - case 8 - pag.5/7                  | 198 |

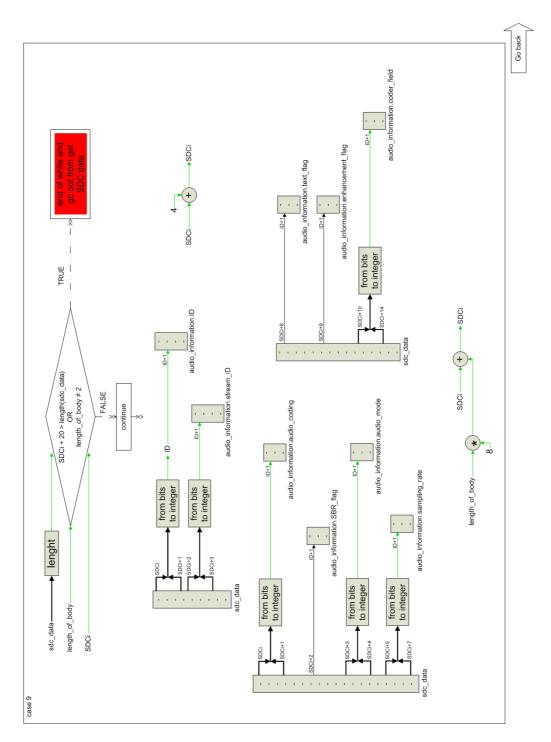

| Figura 147: Get SDC data - case 9 - pag.6/7                  | 199 |

| Figura 148: Get SDC data - case 12 - pag.7/7                 | 200 |

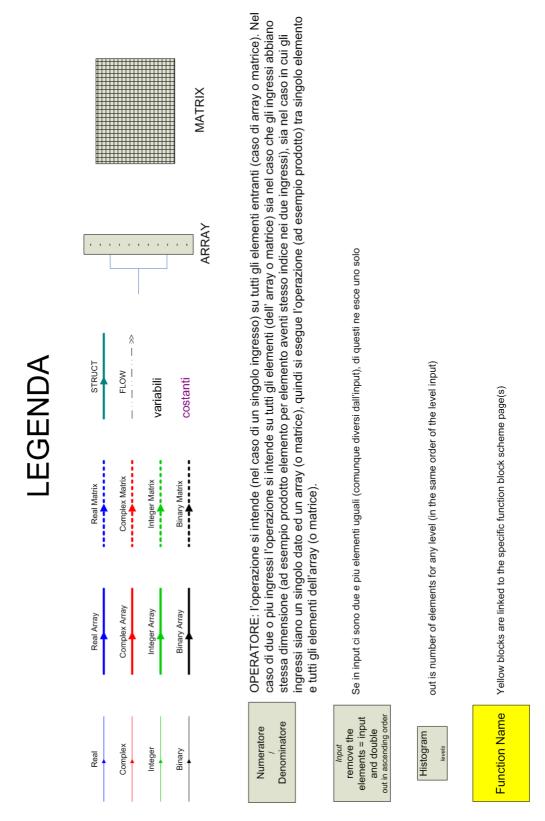

| Figura 149: Legenda breakdown                                | 201 |

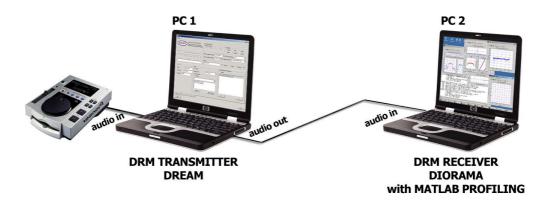

| Figura 150: Strumentazione e connessioni per il Profiling    | 203 |

| Figura 151: Profiling per 60 sec. di DIORAMA                 | 204 |

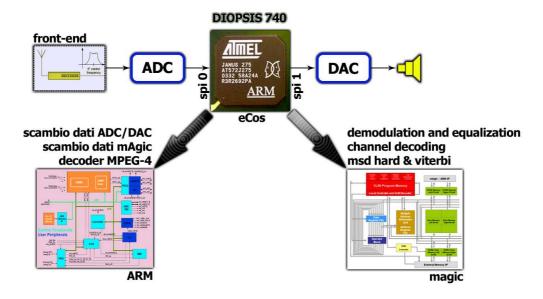

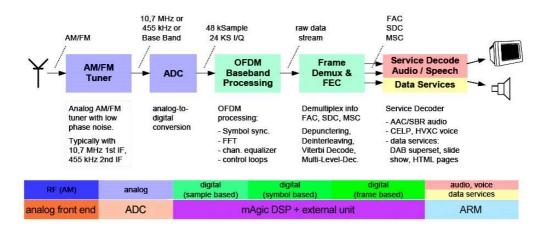

| Figura 152: Ipotesi implementativa su DIOPSIS740             | 208 |

| Figura 153: Complessità AAC su ArM9                          | 209 |

| Figura 154: Caratteristiche della libreria AAC plus per ARM  | 210 |

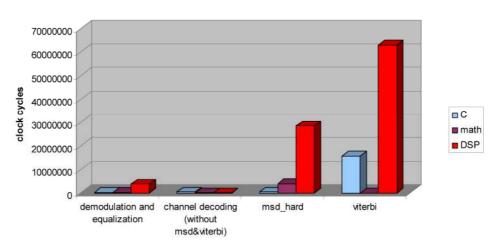

| Figura 155: Cicli di clock per demodulation and equalization | 215 |

| Figura 156: Cicli di clock per channel decoding              | 218 |

| Figura 157: Cicli di clock per get OFDM symbol sync          | 222 |

| Figura 158: Cicli di clock per CRC-8/16                      | 223 |

<u>Indice</u> 9

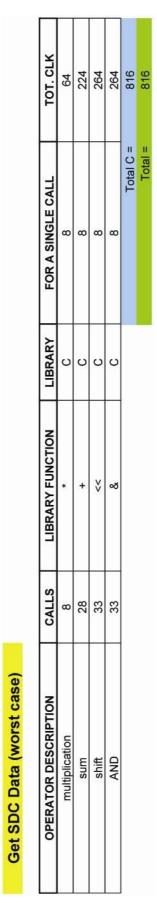

| Figura 159: Cicli di clock per get SDC data                             | 224 |

|-------------------------------------------------------------------------|-----|

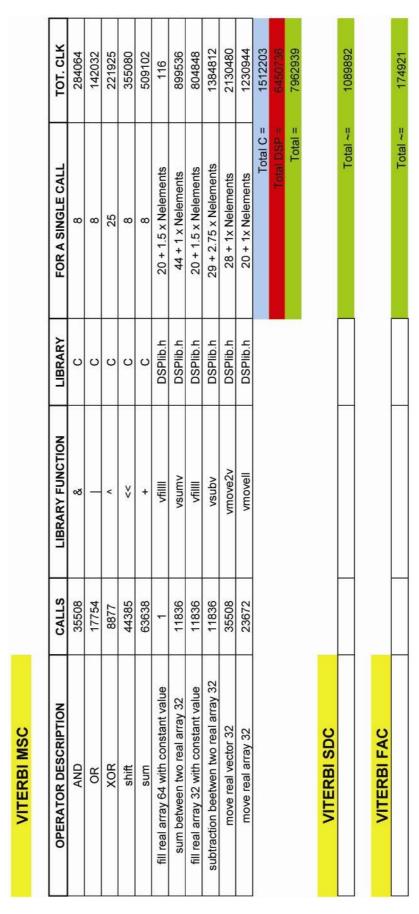

| Figura 160: Cicli di clock per msd hard MSC                             | 225 |

| Figura 161: Cicli di clock per msd hard SDC                             | 226 |

| Figura 162: Cicli di clock per msd hard FAC                             | 227 |

| Figura 163: Cicli di clock per viterbi                                  | 228 |

| Figura 164: Tabella riassuntiva dei cicli di clock necessari            | 229 |

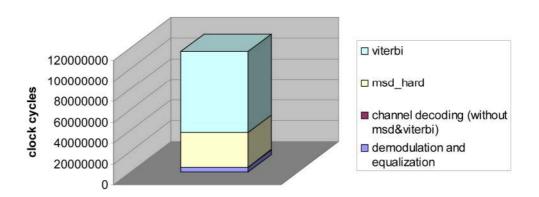

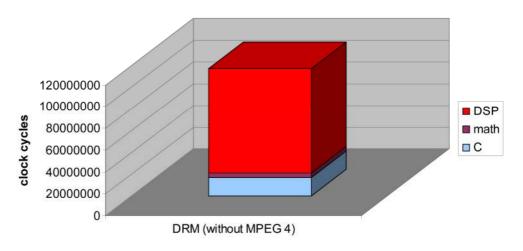

| Figura 165: Istogramma sovrapposto dei cicli totali divisi per funzione | 230 |

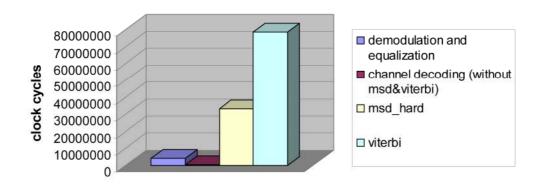

| Figura 166: Istogramma dei cicli totali divisi per funzione             | 230 |

| Figura 167: Istogramma dei cicli totali divisi per libreria utilizzata  | 231 |

| Figura 168: Istogramma dei cicli divisi per funzione e per libreria     | 231 |

| Figura 169: Implementazione ottimale                                    | 234 |

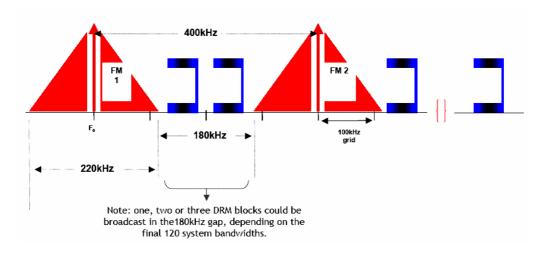

| Figura 170: Sfruttamento con il DRM+ della banda inutilizzata           | 237 |

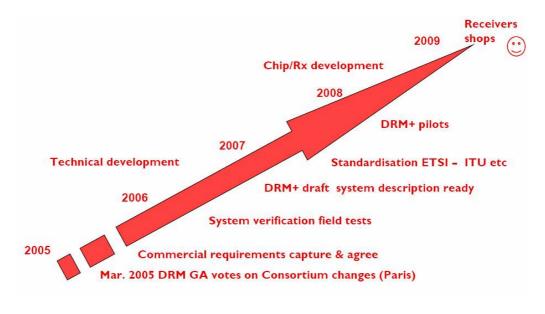

| Figura 171: DRM+ timeline                                               | 237 |

Introduzione 10

### Introduzione

Negli ultimi decenni le innovazioni tecnologiche nel campo dell'elettronica, delle telecomunicazioni e dell'informatica hanno portato alla nascita di innumerevoli nuovi sistemi di comunicazione che sono andati ad affiancarsi a quelli che per decenni hanno dominato la scena mondiale di largo consumo, ovvero radio e televisione analogiche e telefonia fissa. Tutto ciò ha portato innumerevoli vantaggi, sotto i più diversi punti di vista, sia per l'utente che per gli operatori del settore. La presenza della telefonia mobile, della rete internet, e delle telecomunicazioni digitali, sia terrestri che satellitari, non è andata a concorrere con i sistemi di comunicazione tradizionali, come alcuni preannunciavano, ma ha semplicemente ampliato l'offerta per l'utente, spingendo quindi i produttori di hardware a presentare dispositivi in grado di integrare il più alto numero di funzionalità, anche di diversa natura e specie.

Radio e televisione non essendo state quindi sostituite da broadcasting internet o satellitari, stanno subendo una sorta di aggiornamento in quanto i tradizionali sistemi di ricetrasmissione sono oramai obsoleti se paragonati alle tecnologie disponibili oggi. Un esempio è quello della televisione digitale terrestre (DVB-T o DTT), che ha oggi affiancato il tradizionale sistema di trasmissione per arrivare un giorno a sostituirlo totalmente. I vantaggi di tale sostituzione non sono solamente quelli percepibili dagli utenti (maggior numero di canali, più servizi interattivi, migliore qualità), ma sono soprattutto quelli da parte degli operatori, che ottengono tutta la quella serie di vantaggi indotti dal passaggio dall'analogico al digitale.

Per quello che riguarda il panorama radio, nonostante l'introduzione di ricevitori digitali (più piccoli, economici ed efficienti), la trasmissione del segnale utilizza ancora le tecniche di modulazione di ampiezza (AM) e modulazione di frequenza (FM). In un incontro tenutosi a Parigi nel settembre del 1996 tra alcune delle più grandi emittenti e costruttori di apparti, tra cui

Introduzione 11

Radio France, Deutsche Welle, Voice of America e Thomcast, si capì che i giorni per la radiodiffusione, sia nazionale che internazionale, con la tradizionale modulazione AM sotto i 30 MHz erano vicini alla fine. Da questo incontro e da successivi incontri nacque un nuovo organismo: il DRM. Obiettivi di tale organo sono quelli di formulare un progetto per la radiodiffusione digitale nelle onde corte e medie, in modo da definire degli standard mondiali che possano guidare il mercato e l'orientamento dei potenziali utenti, e facilitare la diffusione della tecnologia digitale di modulazione di ampiezza QAM in tutto il mondo. DRM, acronimo di Digital Radio Mondiale, è il nome che ha preso anche questo sistema di radio trasmissione, approvato dall' ITU (International Telecommunication Union), dall'IEC (International Engineering Consortium) e dall' ETSI (European Telecommunications Standard Institute). Quindi il DRM è, al giorno d'oggi, l'unico sistema mondiale di trasmissione non proprietario previsto per le onde corte, medie e lunghe ed in grado di utilizzare le stesse frequenze attualmente assegnate al servizio di radiodiffusione in AM nello spettro fino a 30 MHz, con qualità pari a quella MP3, e può integrare anche dati, testo e immagini.

Nonostante sia presente uno standard ETSI per il DRM, questo non riporta alcuna specifica sul ricevitore che effettua la decodifica di tale segnale. La complessità di calcolo di un ricevitore DRM non è banale, quindi è di estrema importanza scegliere il target su cui implementarlo (ASIC, DSP, FPGA, SOC), tenendo conto che tale scelta influenza notevolmente anche il prezzo finale all'utente.

Lo scopo di questa tesi è quello di studiare l'algoritmo di decodifica a basso livello, al fine di metterne alla luce peculiarità e caratteristiche, per capire che potenza di calcolo è necessaria avere sulla piattaforma su cui si vuole implementare il ricevitore. In particolare verranno analizzate la possibilità di implementazione su un DSP avanzato come il DIOPSIS 740 della ATMEL, le eventuali modifiche hardware da applicare sulla successiva generazione di DIOPSIS per poter effettuare la decodifica in tempo reale. Tutto ciò tenendo

Introduzione 12

presente che il target scelto per l'implementazione presenta caratteristiche adeguate per un'ipotetica e futura diffusione su mercato di larga scala.

## Capitolo 1

### Il Digital Audio Broadcasting (DAB)

#### 1.1 Panoramica attuale sui sistemi DAB

Il Digital Audio Broadcasting è la più importante innovazione nel campo della radiodiffusione dopo l'introduzione della stereofonia in Modulazione di Frequenza. Come l'avvento del Compact Disc negli anni '80 ha rivoluzionato la produzione discografica, così il DAB sta attualmente cambiando la radio e continuerà a farlo anche nei prossimi anni. Alla base di questo nuovo sistema di radiodiffusione vi è la possibilità di offrire all'utente una qualità sonora migliore, anche in condizione di difficile ricezione mobile. Il primo sistema DAB è stato sviluppato in Europa, nell'ambito del progetto EUREKA EU-147, da un consorzio di industrie elettroniche, broadcaster, network provider ed istituti di ricerca. La radiodiffusione FM fu introdotta e pianificata per offrire un buon livello qualitativo d'ascolto agli utenti dotati di un ricevitore fisso con antenna direttiva. Il sovraffollamento della banda e la rapida diffusione dei ricevitori portatili e delle autoradio, hanno messo in evidenza i limiti della ricezione FM (principalmente a causa dell'insorgere di fenomeni come il fading e l'effetto Doppler dovuto al moto relativo tre ricevitore e trasmettitore).

Oltre al sistema Eureka 147, dopo alcuni anni, si sono affacciati sullo scenario mondiale altre tipologie di radiodiffusione digitale terrestre, satellitare o ibrida. I vari sistemi esistenti o in fase di lancio si diversificano tra loro sia per aspetti tecnologici, che per il mercato a cui si rivolgono: il DRM (Digital Radio Mondiale) destinato a rimpiazzare l'attuale diffusione AM, i sistemi Satellite Radio ed IBOC (In Band On Channel) (iBiquity) pensati per il mercato

statunitense, il sistema statunitense Satellite Digital Audio Radio Service (SDARS) ed il sistema WorldSpace che si sta diffondendo nei paesi in via di sviluppo. Questi sistemi di Digital Audio Broadcasting possono differenziarsi per la banda radio in questione o per altre caratteristiche tecniche, ma sono tutti derivanti da Eureka 147, in quanto l'idea di base, la codifica, la modulazione e i vantaggi apportati sono simili tra loro. Nella figura sottostante sono messe a confronto alcuni tra i sistemi DAB terrestri, dei quali verranno sinteticamente presentate le principali caratteristiche nei paragrafi seguenti.

|                                        | Eureka DAB        | ISDB-T (Japan)                   | HD Radio (USA)                      | DRM                                |

|----------------------------------------|-------------------|----------------------------------|-------------------------------------|------------------------------------|

| System Status                          | Open standard     | Open Standard?                   | Proprietary<br>/closed              | Open standard                      |

| Spectrum<br>required                   | 1700kHz           | Variable:<br>430kHz<br>minimum   | 30kHz (MF)<br>400kHz (FM)           | Variable<br>5/10/20kHz             |

| No of digital<br>services<br>supported | 5 to 8 stereo     | 1 -2 stereo very<br>high quality | MF: one stereo<br>FM: 1 to 2 stereo | LF/MF/HF:<br>one stereo            |

| Net bit-rate                           | Variable c. 1Mb/s | c. 280-650kb/s                   | ?                                   | Variable<br>c. 18kb/s to<br>48kb/s |

Figura 1: Confronto tra alcuni sistemi DAB

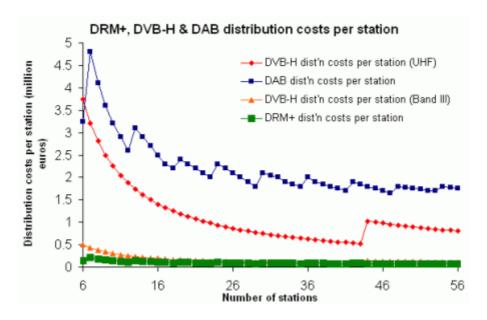

Nella figura sottostante sono illustrati i costi di distribuzione del segnale per sistemi DAB in base alla banda utilizzata ed in base al numero di emittenti. Tale grafico mostra chiaramente che il DRM e il DVB-H in Banda III sono nettamente le soluzioni più economiche per la distribuzione del segnale radio digitale. Ciò è dovuto al fatto che la potenza richiesta per il trasmettitore, a parità di copertura, è tanto più bassa quanto è più è bassa la frequenza utilizzata. Il DRM risulta quindi il sistema più economico e più flessibile, inoltre è quello che sfrutta al meglio la banda, avendo una occupazione

spettrale minima. Tutti questi vantaggi portano di sicuro ad una maggiore complessità del sistema DRM rispetto agli altri tipi di radio digitale.

Figura 2: Costo di distribuzione dei segnali DAB

#### 1.1.1 Eureka 147

Il sistema di radiofonia digitale sviluppato nell'ambito del progetto Europeo Eureka 147 e standardizzato dal European Telecommunications Standards Institute (ETSI) permette la trasmissione di programmi radiofonici digitali ad alta qualità. Il progetto Eureka 147 è stato un consorzio formato dai principali produttori di elettronica di consumo, dai principali enti radiofonici ed istituti di ricerca europei. Fondato nel 1987 nell'ambito del progetto tecnologico "Eureka" finanziato dalla Comunità Europea ha definito le basi per questa importante rivoluzione tecnologica Grazie all'uso della tecnologia digitale il sistema Eureka 147 fornisce agli ascoltatori ed alle stazioni radio vantaggi potenziali e significativi, nonché nuove opportunità. Il sistema è ormai consolidato come standard Europeo e si stà imponendo anche su scala internazionale.

Eureka 147 opera in banda III, tra 174 e 240 MHz e in banda L da 1452 a 1492 MHz, ma può anche operare nelle bande UHF in alcune nazioni. In questo sistema diverse stazioni radio condividono lo stesso segnale, multiplexando insieme i loro bit stream audio, i quali verranno successivamente demultiplexati dal ricevitore.

Eureka 147 DAB è un sistema affidabile e per la radiofonia digitale, progettato per garantire una ottima ricezione in qualunque condizione per ricevitori mobili (autoradio), portatili (Walkman) e fissi (sintonizzatori, hi-fi, etc.), utilizzando una semplice antenna a stilo non-direzionale. Gli aspetti tecnologici fondamentali sono:

- la compressione audio MUSICAM<sup>®</sup>.

- la codifica della trasmissione e la multiplazione.

- la modulazione COFDM.

#### 1.1.2 iBiquity Digital's IBOC

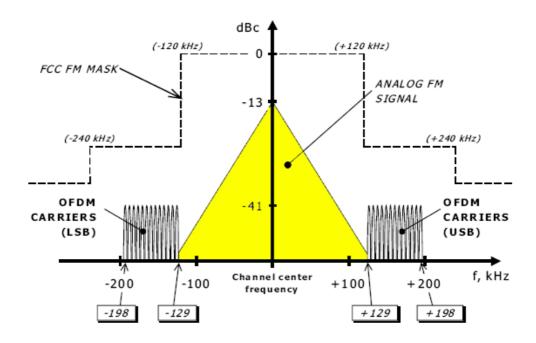

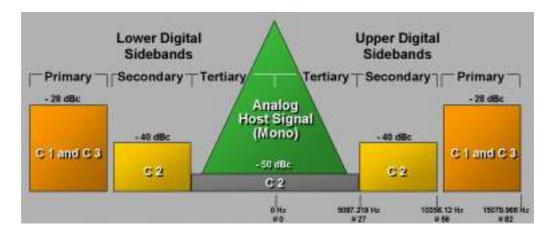

IBOC (In Band On Channel) è il sistema di trasmissione radio digitale, proprietario della iBiquity, utilizzato negli USA, ed è stato studiato per far coesistere nelle stesse bande sia i vecchi segnali analogici, che i nuovi segnali digitali.

Il sistema Eureka 147, originariamente preso in considerazione dagli stati Uniti, è apparso in seguito inadeguato alla congestionata situazione dell'emittenza americana, in pratica non si sarebbe potuto offrire un canale ad ognuno dei molti broadcasters del Paese. Sarebbe stato in ogni modo impossibile allocare la banda necessaria al sistema DAB, infatti, negli Stati Uniti tale porzione di spettro, non risulta libera come nel caso europeo. Alla luce di queste considerazioni è stato sviluppato il concetto di radio diffusione digitale in-band/on-channel, che permette di trasmettere un segnale digitale disponendolo a lato della banda utilizzata dai segnali analogici, sia AM che FM. Così facendo è possibile irradiare un segnale digitale senza occupare

porzioni di banda già destinate ad altri scopi, inoltre è garantita la stessa copertura disponibile per i segnali AM ed FM utilizzando i trasmettitori già installati sul territorio. Inoltre con l'adozione di questo sistema non si costringono le emittenti alla coordinazione necessaria nella trasmissione DAB per la condivisione della risorsa radio. Il sistema IBOC rappresenta inoltre un modello per la transizione graduale al digitale, infatti, i ricevitori attualmente in commercio possono ricevere tranquillamente la porzione analogica del segnale mentre apparati più moderni possono lavorare con la parte digitale. Nonostante i problemi riscontrati nei primi anni (specie con la parte di segnale analogico) è attualmente in funzione una seconda versione di IBOC che non presenta più tali problemi e studiata appositamente per una graduale, ma totale, transizione dall'analogico al digitale.

Le figure sottostanti mostrano degli schemi di principio su come IBOC utilizza le bande sia AM che FM.

Figura 3: iBiquity FM IBOC system

Figura 4: iBiquity FM IBOC Hybrid system

Come per gli altri sistemi DAB, anche IBOC è stato pensato per migliorare la qualità audio, per eliminare le interferenze, per combattere il problema del multipath, con soluzioni del tutto analoghe a quelle degli altri sistemi di radio digitale.

#### 1.1.3 ISDB-T

ISDB-T (Terrestrial Integrated Services Digital Broadcasting) è un tipo di broadcasting per servizi multimediali, sviluppatosi in Giappone, e può essere utilizzato sia per canali radio, sia per canali TV, logicamente con differenti larghezze di banda. Le caratteristiche principali di questo broadcasting sono:

- Compressione MPEG-2 del segnale utile da trasmettere.

- Uso flessibile degli schemi di mudulazione, ovvero i contenuti possono essere trasmessi di volta in volta con il bit rate più appropriato.

- Presenza di segnali di controllo che informano il ricevitore sulle configurazioni di multiplexing e di modulazione.

- Ricezione parziale dei servizi, implicando così una minore complessità per il ricevitore.

L'ISDB-T può essere applicato sia alla TV, DTTB (Digital Terrestrial Television Broadcasting), che alla radio DSB (Digital Sound Broadcasting),

oppure è anche possibile un mix tra i due servizi ed altri servizi multimediali. Il sistema trasmissivo adottato anche in questo caso è analogo a quelli precedentemente descritti: compressione audio, multiplexing, OFDM, dove ogni segmento ha larghezza di banda pari a B/14 MHz (B = 6, 7, o 8 MHz).

#### 1.1.4 Satellite Digital Audio Radio Services

Oltre ai sistemi DAB terrestri esistono anche quelli satellitari. Negli USA grazie al sistema SDARS (Satellite Digital Audio Radio Services) gli ascoltatori potranno ricevere molte stazioni radio ovunque nel Paese, anche in movimento nella propria auto, cosa fino ad ieri aveva creato non pochi problemi ai gestori dei precedenti sistemi di radiodiffusione.

Due sistemi SDARS statunitensi operano diffondendo le loro trasmissioni commerciali: Sirius Satellite Radio Inc. di New York City e XM Satellite Radio di Washington D.C. I due sistemi operano con alcune caratteristiche in comune, come il numero di canali, ed altre completamente diverse, come le orbite scelte dai due gestori: i satelliti di XM sono geostazionari, mentre quelli di Sirius descrivono un'orbita. I tre satelliti di Sirius seguono un percorso simile ad "otto deformato" sopra il continente americano, in cui la pancia che giace sulla parte settentrionale è più piccola di quella meridionale. Questa particolare deformazione conferisce una proprietà interessante agli stessi satelliti: infatti in un periodo di ventiquattro ore ognuno di essi "sorge" (dall'equatore), sorvola gli Stati Uniti per sedici ore e "tramonta" sotto l'equatore per ripresentarsi dopo otto ore. In questo modo, due dei tre satelliti sono sempre sopra al Nord America assicurando la copertura degli Stati Uniti e garantendo un servizio, che, specialmente nelle aree rurali la copertura terrestre non potrà mai eguagliare.

Sia Sirius che XM hanno deciso di integrare la loro rete satellitare con ripetitori a terra per reirradiare il segnale SDARS così da permettere la copertura di alcuni siti, particolarmente difficili da raggiungere come gallerie o canyon urbani, conferendo un carattere ancora più marcato alla diversificazione del sistema. Sui ripetitori terrestri vengono usate tecniche di trasmissione diverse da quelle usate sui satelliti. La tecnica di trasmissione usata a terra è la OFDM, mentre a bordo dei satelliti si implementa una QPSK con multiplazione a divisione di tempo.

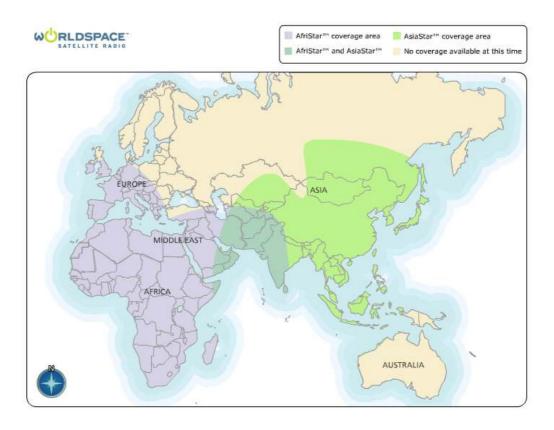

#### 1.1.5 WorldSpace

La Compagnia Worldspace è stata fondata nel 1990 con lo scopo di diffondere il segnale radiofonico digitale ed alcuni servizi dati primariamente ai paesi in via di sviluppo situati in Africa, Medio Oriente, Asia, America Latina e Caraibi.

La costellazione WorldSpace è costituita da due satelliti geostazionari: AfriStar e AsiaStar. Ognuno dei due satelliti è equipaggiato con tre illuminatori, che con i loro fasci diffondono oltre 120 canali audio (con qualità sonora cristallina) e svariati servizi internet pensati per la ricezione tramite apparecchi portatili. I vantaggi introdotti da questa nuova tecnologia sono principalmente i seguenti:

- Scelta: attualmente nessun altro media dispone della varietà di programmi offerti da WorldSpace, inoltre ogni ricevitore è fornito di una porta dati che lo rende un vero e proprio modem in grado di un PC a molte funzioni Internet.

- Qualità sonora: la digitalizzazione rende il segnale immune da fading e disturbi di vario genere, il sistema fornisce una qualità audio vicina a quella del CD, accessibile ovunque all'interno delle aree di copertura.

- Copertura: oltre quattordici milioni di chilometri quadrati sono illuminati dai satelliti (con qualità sonora elevata)

Essendo WorldSpace una compagnia statunitense, il servizio offerto è disponibile per tutti i paesi al di fuori di quelli che per diverse ragioni politiche non hanno rapporti con gli USA. La figura sottostante mostra la copertura dei due satelliti.

Figura 5: Copertura dei satelliti Worldspace

#### 1.1.6 Digital Radio Mondiale

Il DRM, acronimo di Digital Radio Mondiale, è sia il nome del consorzio di aziende che hanno studiato tale tipo di broadcasting digitale per la banda AM, sia il nome del sistema trasmissivo, standardizzato dall' ETSI. Caratteristiche, peculiarità e vantaggi saranno analizzate in dettaglio nel prossimo capitolo.

#### 1.2 Vantaggi dei sistemi DAB

La Radio Digitale è l'evoluzione più significativa nella tecnologia radiofonica dall'introduzione delle trasmissioni stereo in MF. Annuncia una rivoluzione per la diffusione dei servizi radiofonici offrendo innumerevoli vantaggi: agli ascoltatori, agli editori radiofonici, agli organi governativi competenti in materia di assegnazione e gestione dello spettro radioelettrico. Quest'ultimo aspetto è per molti irrilevante, ma è cruciale per una gestione efficiente dello spettro radio, risorsa non infinita e preziosa. I principali benefici offerti dalla radio digitale sono:

- La ricezione sicura e continua, libera da interferenze ed immune agli

effetti degenerativi provocati dalla propagazione delle onde radio in

presenza di ostacoli ed echi (cammini multipli), che abbassano

drasticamente la qualità di ricezione in modulazione di frequenza, e

consentendo l'ascolto dell'audio digitale ad alta qualità anche nelle

condizioni più difficili.

- Ricevitori facili da usare: non è più necessario sintonizzare di nuovo il programma ascoltato spostandosi da una zona all'altra, e la memorizzazione dei programmi è effettuata dal ricevitore stesso.

- Servizi aggiuntivi permetteranno il miglioramento dei servizi già esistenti basati sull'audio e l'opportunità per l'introduzione di servizi innovativi. L'elevata capacità di trasmissione dati della Radio Digitale permette l'inserimento di informazioni associate ai programmi o indipendenti da questi, ad un livello estremamente superiore a quanto oggi disponibile con il Radio Data System (RDS) presente nella radio in modulazione di frequenza. Questi dati possono essere sfruttati per informazioni sul traffico estremamente dettagliate, per scaricare aggiornamenti su sistemi di navigazione ed altro.

- L'uso efficiente dello spettro elettromagnetico. Più programmi condividono la stessa porzione di banda a radiofrequenza essendo opportunamente canalizzati in un unico flusso digitale. La maggiore flessibilità per le stazioni radio si traduce in una maggiore scelta per gli ascoltatori. L'uso di reti di diffusione isofrequenziali (SFN Single frequency network), in cui tutti i trasmettitori parte della stessa rete operano sulla stessa frequenza, permette di non dover cambiare la frequenza di ricezione spostandosi da una zona all'altra.

- La multiplazione di più programmi su un unico canale radio resasi disponibile dalla tecnologia digitale consente un ascolto ottimale anche con una riduzione della potenza irradiata dai trasmettitori.

- Flessibilità e ampie possibilità di scelta, grazie ad un sistema che è essenzialmente un unico flusso di dati che può quindi trasmettere numerose tipologie di servizi. Questi possono includere: programmi audio già esistenti con l'aggiunta di informazioni sotto forma di testi, grafica o elementi multimediali; servizi radiofonici completamente nuovi, come servizi dati indipendenti o applicazioni specificatamente multimediali, oppure un mix degli elementi elencati sopra.

#### 1.3 Reti SFN

Una delle caratteristiche della radio digitale è quella di avere la possibilità di utilizzare la stessa frequenza per coprire grandi aree, come nazioni o anche interi continenti. Questo è possibile grazie a tecniche di modulazione del segnale che sono immuni alle interferenze che si generano quando il ricevitore si trova in un area coperta da più di un antenna trasmittente. Per coprire grandi aree, come ad esempio una nazione, l'infrastruttura richiesta consiste di un gran numero di trasmettitori disposti in maniera quasi regolare. Trasmettitori

adiacenti devono usare frequenze differenti quando irradiano lo stesso programma per evitare interferenza al ricevitore. Per ridurre il costo dell'infrastruttura è preferibile avere una bassa densità di trasmettitori, tuttavia un trasmettitore può servire solo un'area limitata a causa della struttura sferica della terra per qui i ricevitori che si trovano di là dell'orizzonte radio subirebbero un forte degrado di potenza ricevuta vedendo così la qualità del offerto fortemente ridotta. Nella fornitura di servizi telecomunicazioni per un gran numero di programmi il limite principale è la carenza di spettro radiofrequenziale, perciò è essenziale usare tale spettro in modo efficiente. Un approccio fondamentale per raggiungere un'elevata utilizzazione di banda consiste nel riutilizzare lo spettro in aree geografiche separate, in modo tale che un trasmettitore non risenta dell'interferenza causata da un altro trasmettitore che opera sulla stessa frequenza. Quest'aspetto della progettazione di rete richiede un'opportuna strategia di pianificazione del riuso delle frequenze, una possibile strategia è mostrata in figura.

Figura 6: Cluster convenzionale a 7 celle

Attualmente si sta sviluppando un nuovo tipo di sistema di trasmissione, capace di servire un'area arbitrariamente grande con lo stesso programma senza dover riutilizzare le frequenze, la rete così costruita prende il nome di Rete Isofrequenziale o SFN (Single Frequency Network).

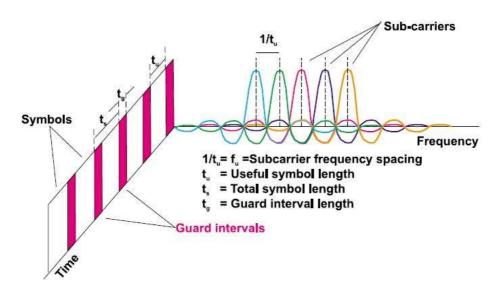

Le reti SFN (single frequency network), ovvero isofrequenziali, esigono altri requisiti di copertura. La probabilità di copertura di una rete, definita come la probabilità che un ricevitore posizionato a caso all'interno dell'area di servizio possa ricevere il programma trasmesso con la desiderata qualità, cioè che il rapporto segnale-disturbo sia superiore ad una prefissata soglia, essendo tale soglia derivata dalla potenza di rumore e dall'interferenza, deve avere per essere giudicata soddisfacente, un valore maggiore del 90%, riducendo così a pochi punti percentuali la complementare probabilità di servizio non disponibile. Un limite fondamentale delle reti isofrequenziali e che i segnali provenienti da trasmettitori molto lontani possono causare interferenza intersimbolica piuttosto che contributo utile. Un parametro molto importante per controllare tale problema è l'intervallo di guardia tra due simboli consecutivi OFDM.

Le prestazioni nei sistemi digitali, e non solo, dipendono dal rapporto tra segnale utile e segnale di disturbo e per un utilizzo efficiente dello spettro il progetto della rete dovrà focalizzarsi sul massimizzare questo rapporto.

L'EBU (European Broadcasting Union) ha fornito un metodo per il calcolo della probabilità di copertura. Risultati sperimentali hanno dimostrato che è possibile ottenere un'ottima copertura (>99%) per reti nazionali. Inoltre, già a potenze modeste, come 100 W/programma DAB, il sistema diventa limitato dalla propria interferenza e non si ottengono quindi miglioramenti incrementando ulteriormente il livello di potenza.

#### 1.4 La modulazione OFDM

Uno dei problemi più gravosi che affligge la ricezione di segnali FM è la eccessiva sensibilità che sistemi analogici evidenziano nei confronti dei cammini multipli. Questo fenomeno ha infatti la capacità, in particolari

condizioni, di distorcere a tal punto il segnale da renderlo di fatto incomprensibile.

Figura 7: Multi-Path propagation

Il sistema di modulazione numerico OFDM (Multiplazione a Divisione di Frequenza Ortogonale) consente di contrastare l'interferenza dovuta ai cammini multipli. Inoltre essendo tutte le portanti ortogonali si evita anche l'interferenza tra due portanti vicine e non è necessario un banco di filtri passa banda molto selettivi in fase di ricezione per isolare le singole portanti. In questo tipo di multiplazione un flusso di dati ad alta velocità è modulato su un gran numero di segnali ortogonali a banda stretta che sono successivamente multiplati in frequenza. Il basso bit rate di ogni portante e l'inserzione di un intervallo di guardia tra due simboli consecutivi OFDM consente di controllare efficacemente il problema dell'interferenza intersimbolica.

Per quanto riguarda gli errori sui dati causati dal canale selettivo in frequenza, si può provvedere per mezzo di potenti codici a correzione d'errore. In figura è rappresentato lo schema di principio di trasmissione e ricezione di un segnale OFDM. È facilmente intuibile che tutta la serie di benefici introdotti da tale metodo hanno come contro una più elevata complessità computazionale rispetto ai metodi tradizionali, sia per l'apparato trasmittente che per quello ricevente, dovuto alla necessita di effettuare la Fast Fourier Transform, sia in trasmissione che in ricezione.

Figura 8: The OFDM link functions

Nella distribuzione di un programma su un certo numero di trasmettitori, lo schema OFDM non richiede che essi usino frequenze differenti e quindi tutti i trasmettitori della rete trasmettono in contemporanea la stessa informazione sulla medesima frequenza. E' a questo punto chiaro che un ricevitore sarà soggetto alla propagazione di diversi cammini multipli artificiali, ovvero quelli prodotti dalla presenza di più trasmittenti alla stessa frequenza sul territorio.

Se il ricevitore è in grado di superare questo inconveniente, possono essere compiuti sostanziali miglioramenti nell'efficienza spettrale. Ciò è molto suggestivo per le reti nazionali, visto che non è più necessario il riuso della frequenza, tuttavia nel dimensionamento di una rete nazionale reale occorrerà considerare anche la presenza di altre reti che possono coesistere, ad esempio ai confini, per questo si avrà una leggera riduzione dell'efficienza spettrale.

## Capitolo 2

# **DRM: Digital Radio Mondiale**

#### 2.1 Il consorzio DRM

Il DRM venne alla luce durante un incontro a Parigi nel settembre del 1996, tra alcune delle più grandi emittenti e costruttori di apparti. Vi erano rappresentanti di Radio France, Deutsche Welle, Voice of America e Thomcast. Durante questo raduno tutte le parti concordarono su un punto: i giorni per la radiodiffusione, sia nazionale che internazionale, con la tradizionale modulazione AM sotto i 30MHz, erano vicini alla fine.

Nel novembre dello stesso anno, ebbe luogo un altro incontro al quale partecipò un gruppo più ampio di aziende interessate, incluse emittenti ed operatori in AM, nazionali ed internazionali, centri di ricerca, produttori di apparati ricevitori e organizzazioni che mirano allo sviluppo di una nuova diffusione digitale in Banda AM. Da questo incontro nacque un nuovo organismo, DRM (Digital Radio Mondiale), i cui obiettivi sono:

- Formulare un progetto per la radiodiffusione digitale in Banda AM, in modo da definire degli standard mondiali che possano guidare il mercato e l'orientamento dei potenziali utenti.

- Facilitare la diffusione della tecnologia digitale AM in tutto il mondo.

Furono formati tre gruppi di lavoro, incaricati di studiare e preparare progetti e raccomandazioni, da sottoporre all'attenzione dei partecipanti ai futuri incontri del DRM:

- Un gruppo (Broadcast Requirement Workgroup) per stabilire una bozza di documento dei requisiti per la diffusione.

- Un gruppo per stabilire le raccomandazioni per l'organizzazione (Iterim Steering Board).

- Un terzo gruppo (Conference Group) per creare le premesse per un congresso mondiale sulla radiodiffusione digitale in Banda AM.

Il 4 aprile del 1997, a Las Vegas (Nevada, Stati Uniti), ebbe luogo il primo incontro formale di Digital Radio Mondiale a cui parteciparono oltre quaranta delegazioni appartenenti a diversi settori industriali interessati e a molti Paesi del mondo, durante il quale fu deliberato che:

- Il documento elaborato dal gruppo incaricato di raccogliere i requisiti per la diffusione (Broadcast Requirement Workgroup) fu accolto.

- Con piccoli e non sostanziali cambiamenti questo documento potesse essere reso disponibile all'intera comunità mondiale.

- Questo documento avrebbe rappresentato un primo passo verso un vero e proprio protocollo commerciale.

Le raccomandazioni dell'Iterim Steering Board, furono recepite con i seguenti risultati:

- Le raccomandazioni sull'organizzazione formale del DRM furono accettate ed i principi contenuti nel memorandum d'intesa (MoU) approvati.

- Fu formato un nuovo gruppo di lavoro per definire le raccomandazioni al prossimo incontro dello Steering Board, per ampliare il MoU (Confidentiality and Intellectual Property Rights).

- Fu formato un nuovo gruppo di lavoro (Marketing Group), per collaborare con il Commercial Committee allo scopo di promuovere commercialmente il DRM a livello mondiale.

Nell'agosto del 1997, in occasione del terzo meeting di DRM svoltosi durante IFA97 a Berlino quarantotto delegazioni si incontrarono ed approvarono i seguenti punti:

- Rapporto di Thomcast, ZRA/DTAG, IBB/JPL e NADIB sullo stato dello sviluppo dei sistemi da loro proposti.

- Rapporto del gruppo di lavoro "Confidentiality and Inellectual Property Rights".

- Forma finale del memorandum d'intesa MoU.

Il 5 marzo 1998, venti dei maggiori broadcaster mondiali firmarono il "Digital AM Memorandum of Understanding" a Guangzhou (ex Canton) in Cina.

È bene specificare che il sistema DRM non è in competizione con il DAB, piuttosto i due si completano e possono essere usati parallelamente. Si pensi che il primo sistema si avvale dell'uso delle frequenze destinate all'AM ed è in grado di servire grandi aree e lunghe distanze, vedremo nel seguito che si raggiungono senza particolari problemi distanze superiori ai 7000 Km, diversamente da ciò che accade nel DAB, che ha la capacità di coprire tipicamente aree nazionali o regionali avvalendosi di reti SNF a diffusione, talvolta, molto capillare sul territorio.

Figura 9: Logo del consorzio DRM

A marzo del 2001 il Consorzio poteva contare un totale di 69 membri aderenti, grazie anche all'ingresso di NHK, All India Radio e Voice of Nigeria.

Vale la pena ricordare gli obiettivi che il consorzio ha prefissato e che in questi anni ha cercato di raggiungere:

- Migliorare la ricezione e la qualità dell'audio rispetto all'AM tradizionale.

- Compatibilità con l'attuale allocazione delle frequenze.

- Ricerca di un sistema flessibile per le problematiche odierne e per il futuro.

- Un piano per la transizione dall'analogico al digitale.

- Possibilità di trasmissione dati.

- Massimizzazione del riuso dei preesistenti impianti di trasmissione.

- Pronta disponibilità di apparati ricevitori economici.

I membri del consorzio DRM sono cresciuti negli anni, e attualmente si suddividono in DRM Members, e in DRM Associate Members. In risposta al sempre più crescente interesse nei il consorzio ha creato un nuovo tipo di affiliazione chiamate DRM Supporter. L'Italia attualmente compare solamente tra i DRM Supporter (DB Elettronica Telecommunicazioni SpA, ELAD srl, Sistel, World Family of Radio Maria Association), mentre era presente all'interno dei DRM Members dalla fondazione fino ad alcuni anni fa la RAI Radio Televisione Italiana.

#### Attualmente i DRM Members sono:

Antenna Hungária Hungary ATMEL GMBH Germany UK **British Broadcasting Corporation** USA Broadcast Electronics, Inc. Cadena SER Spain Coding Technologies AB Sweden **USA** Continental Electronics Corporation Deutsche Welle Germany DeutschlandRadio Germany Digidia France Finland Digita Oy UK Digital One Dolby Laboratories Inc USA Europe 1 (C.E.R.T) France Fraunhofer Gesellschaft Institut Integrierte Schaltungen Germany HARMAN/BECKER Automotive Systems GmbH Germany Radio France Internationale

Harris Broadcast USA

Hitachi Kokusai Electric Japan

Imagination Technologies UK

International Broadcasting Bureau – IBB USA

Kintronic Laboratories Inc USA

Libyan Jamahiriya Broadcasting Corp. Libya

Micronas GmbH Germany

Nautel Ltd Canada

NEC Corporation Japan

Nero AG Germany

Nippon Hoso Kyokai Japan

Norkring AS Norway

Nozema Netherlands

Qinetiq UK

Radio Canada International Canada

Radio France France

Radio Nederland Wereldomroep Netherlands

France

Radio Sweden Int. Sweden

Radio Vaticana Vatican City

Radiodifusao Portuguesa Portugal

Radioscape UK

RIZ-TRANSMITTERS Co. Croatia

Robert Bosch GmbH Germany

RTL Group Luxembourg

RTRN & Voice of Russia Russia

Samsung Electronics Co. Ltd. Korea

Sangean America, Inc. USA

Sony International Germany

SWR Südwestrundfunk Germany

T-Systems Business Services GmbH Germany

TCI International, Inc USA

TDF France

TDP Belgium

Texas Instruments USA

Thales Broadcast & Multimedia France

TRANSRADIO SenderSysteme Berlin AG Germany

Voice of Nigeria Nigeria

VT Communications UK

WRN UK

#### Mentre I DRM Associate Members sono:

Broadcasting Center Europe SA (CLT-UFA)

A.P.R Arbeitsgemeinschaft Privater Rundfunk

Academy of Broadcasting Science - ABS

China

ADDX

Germany

Agentschap Telecom

Arab States Broadcasting Union - ASBU

Asia Pacific Broadcasting Union - ABU

Malaysia

Basamad College Iran

CCETT France

Christian Vision United Kingdom

Commercial Radio Australia

Communications University of China

Digital Radios Françaises

DLM-Direktorenkonferenz der Landesmedienanstalten

Australia

China

France

Dolby Laboratories Licensing Corp. USA

ESPOL Ecuador

European Broadcasting Union Switzerland

Generalitad de Catalunya Spain

Georg-Simon-Ohm University of Applied Sciences Germany

HCJB World Radio Ecuador

HFCC Czech Republic

ICRC - International Committee of the Red Cross Switzerland

Institut für Rundfunktechnik - IRT Germany

Luxembourg

International Telecommunication Union - ITU Switzerland Kymenlaakso Polytechnic Finland MSA / Digitaler Rundfunk Sachsen-Anhalt Germany National Association of Shortwave Broadcasters - NASB USA National Communications Authority, Hungary Hungary Radio New Zealand International - RNZI New Zealand **TDP** Radio Belgium The University of Hannover Germany The University of Kassel Germany The University of Ulm Germany The University of Applied Sciences, FH Merseburg Germany TU Delft Netherlands Universidad del Pais Vasco Spain Via Licensing Corp. **USA VPRT** Germany VSP Verband Schweizer Privatradios Switzerland

Figura 10: Nazioni con membri DRM

Nelgi anni successivi fino al 2003 sono stati effettuati molteplici prove per testare il sistema sviluppato, ed il 16 Giugno 2003 è stata inaugurata ufficialmente il primo broadcasting DRM a Ginevra – Svizzera, dutante la World Radio Conference dell ITU. In questa tesi si farà riferimento alle specifiche di sistema del DRM pubblicate ufficialmente nello standard *ETSI ES* 201 980 V2.2.1 (2005-08). Attualmente il consorzio DRM sta cercando di applicare una tecnica simile anche in banda FM, ma ciò e tutt'ora in via di sviluppo, mentre per quel che riguarda il DRM in banda AM, diverse aziende stanno cercando di realizzare ricevitori DRM low cost per il mercato di largo consumo basati su chip DRM, ovvero circuiti integrati studiati appositamente per la ricezione DRM, argomento che verrà ampiamente analizzato nei capitoli successivi.

### 2.2 Attuale utilizzo della banda AM e benefici del DRM

La banda AM ha una gamma di proprietà che la rendono estremamente interessante. In primo luogo si ha un vantaggio nei due modi di propagazione a queste frequenze, ovvero si sfruttano le caratteristiche delle *ground wave* e delle *sky wave*.

La parte a più bassa frequenza, banda LF, detta anche *long-wave band* (LW), è in grado di coprire aree molto vaste (anche più di un'intera nazione) grazie alle ground wave, utilizzando una singola antenna trasmittente. Le onde lunghe implicano grandi dimensione di antenna trasmittente (molto costose). LW è molto diffusa in Europa, ma non è a disposizione per i radio broadcasters in America.

Le medie frequenze (MF), o *medium-wave band* (MW), è disponibile in tutto il mondo, ed è usata per diversi tipi di applicazioni. La propagazione delle ground-waves è leggermente meno efficiente rispetto alla banda LF, ma oggi si

riesce comunque ad assicurare la copertura di un intera nazione anche in banda MF con una singola antenna o al più con una piccola rete di qualche antenna (dipende anche dall'estensione della nazione da coprire). Questa banda è anche utilizzata per coperture locali con singole trasmittenti a bassissima potenza. Durante la notte, quando l'assorbimento del livello D della ionosfera è minore, la propagazione delle sky-wave va in aiuto alle ground wave. Questo può essere visto come un ostacolo o come un aiuto. Infatti l'aumento di propagazione può provocare interferenze a stazioni che usano la stessa frequenza ma in territori lontani (e in tal caso di notte è possibile sentire un segnale audio in background indesiderato). Le sky-wave possono anche generare autointerferenza sulla stessa stazione in quanto arrivano in ritardo rispetto alle ground-wave, generando fenomeni di multipath, che distorcono il suono ricevuto. Il fenomeno delle sky-wave può anche essere visto positivamente, in quanto (specie per i broadcasters internazionali) si riescono a raggiungere aree che le ground-wave non coprono.

La banda HF (o *short-wave band*, SW) è conosciuta principalmente per facilitare il broadcasting internazionale, grazie alle sky-wave, anche a grandissime distanze, in quanto non ci sono ostacoli sul percorso. Il segnale può propagarsi anche su metà globo terrestre, anche se solitamente si usa avere più di un antenna per tale tipo di distribuzione. La parte inferiore della banda SW è usata anche per la copertura di nazioni che si trovano sui tropici o per nazioni molto vaste. Va tenuto conto che la propagazione delle sky-wave dipende dallo stato della ionosfera, che cambia nel corso delle 24 ore, e cambiano nel corso del sunspot cycle (11 anni) con caratteristiche casuali. Per questo i broadcasters in banda HF devono continuamente cambiare frequenza nell'arco del giorno, e nei casi di differenti modi di propagazione (causa grande estensione della nazione da coprire) si usa trasmettere in parallelo su più di una frequenza.

#### I vantaggi del tradizionale metodo AM sono:

Possibilità di copertura nazionale o internazionale con pochi siti trasmessivi necessari.

- È possible realizzare broadcasting internazionale senza l'utilizzo di gatekeepers.

- I ricevitori sono semplici, economici, funzionanti e disponibili in tutto il mondo.

Mentre gli svantaggi dell'attuale sistema AM sono:

- Qualità audio limitata dai moderni standard.

- Frequenti cambi di frequenza (di difficile schedulazione) nel broadcasting in banda HF.

- Scarsa immagine e considerazione se si paragona l'AM alla tecnologia digitale attualmente disponibile.

La tecnologia digitale applicata alla banda AM è in grado di mantenere i tre vantaggi sopra elencati e di eliminare gli svantaggi.

L'attuale sistema AM presenta una scarsa qualità audio a causa della banda molto limitata, quindi per una stazione AM risulta molto difficile competere con chi trasmette in banda FM. Oltre alla larghezza di banda altre limitazioni alla qualità audio sono il limitato rapporto segnale rumore, il fading lento o veloce, il fading selettivo dovuto al multipath, autointerferenza e interferenza con i canali adiacenti e altre interferenze dovute a cause naturali o artificiali. Quindi risulta fondamentale realizzare un segnale robusto a tali effetti.

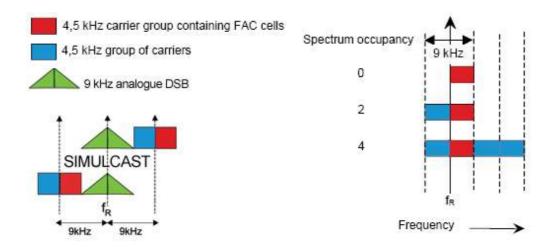

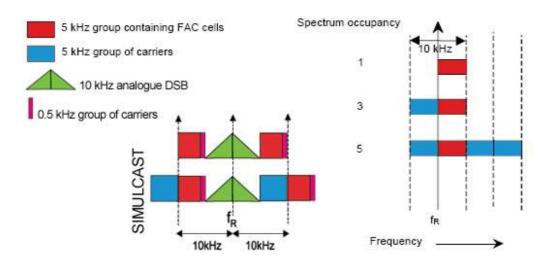

Essendo lo spettro saturo non è possibile allocare una porzione di banda dedicata per il DRM, infatti questo è stato progettato per occupare gli spazi lasciati liberi tra due canali analogici, quindi viene effettuato il Simulcast, ovvero la trasmissione simultanea di due diversi tipi di segnale nella stessa banda. Ogni canale AM ha una banda di 18 kHz dei quali solo 9 sono utilizzati e 9 sono lasciati liberi per evitare interferenze con i canali adiacenti, questi sono utilizzati oggi per il DRM, mediante canali base di 4.5 kHz. Le diverse larghezze di banda possibili permettono il simulcast anche dove la larghezza di un canale AM è di 20 kHz. L'ampiezza del segnale DRM è di 16 dB minore a quello AM per evitare interferenze nella ricezione analogica.

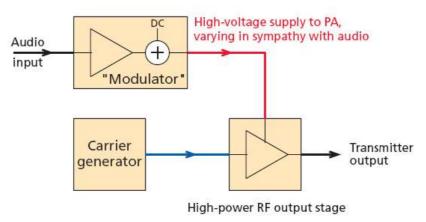

Un altro argomento che va affrontato è quello di studiare la possibilità di convertire gli attuali siti di trasmissione AM in DRM. A tale proposito va detto che esistono diversi tipi di siti trasmessivi, alcuni tecnologicamente molto obsoleti, ma la maggior parte di questi usa una modulazione ad alto livello. L'ampiezza del segnale RF è modulata variando la potenza dell'alimentazione dell'amplificatore non lineare a radio frequenze (come visibile in figura a). È possibile considerare il segnale digitale DRM come un segnale modulato in fase (quindi di ampiezza costante, ma anche con ampiezza non costante non determinerebbe un problema per la ricezione), quindi è possibile separare il segnale DRM in componenti AM e PM. La componente AM si applica dove era precedentemente applicato l'ingresso della modulazione audio, mentre al posto dell' ingresso della portante si applica il segnale RF modulato in fase (come visibile in figura b). La banda del segnale modulato in ampiezza è maggiore di quella del segnale audio, quindi se necessario è possibile aggiungere un filtro per rendere il tutto funzionate.

### (a) Present AM transmitter

#### (b) The same transmitter, converted to digital modulation

Figura 11: Uso delle attuali trasmittenti AM per il DRM

Un'altra caratteristica del DRM è quella di apportare alla banda AM una "user friendliness" precedentemente assente, infatti attualmente un ascoltatore se vuole ascoltare un determinato programma deve conoscere la precisa banda e frequenza, che può cambiare con il tempo e con lo spostamento. Queste informazioni spesso non sono di interesse per l'ascoltatore, che magari vorrebbe poter scegliere il programma in base a criteri tematici. Ciò è possibile con il DRM, ed inoltre una volta sintonizzato un canale saranno subito disponibili informazioni sul tipo di trasmissione radio, ed il ricevitore apprenderà automaticamente come risintonizzare tale stazione in caso di cambio di frequenza trasmissiva. Ovvero si avrà un qualcosa di simile, ma più evoluto, all'RDS anche in banda AM.

Il sistema DRM presenta anche un'altra caratteristica importante. Precedentemente è stato fatto riferimento a tutti i disturbi a cui è soggetto un segnale in banda AM. Questi disturbi divengono più accentuati all'aumentare dell'area da coprire, ad esempio trasmissioni locali tramite ground-wave saranno soggette a minori disturbi rispetto a trasmissioni nazionali che sfruttano anche le sky-wave. Quindi con il DRM i broadcasters saranno in grado di selezionare il grado di robustezza desiderato in base all'applicazione, in modo tale da poter sempre avere un buon matching tra capacità di payload e robustezza del segnale trasmesso ai disturbi.

Quindi è possibile elencare la serie di vantaggi che il DRM è in grado di apportare per gli ascoltatori:

- Qualità audio simile alla FM, sfruttando la ricezione AM. Si ha un bit rate massimo di 25 Kbit/s, con possibilità in futuro di accorpare due canali per poter avvicinarsi alla qualità sonora del CD.

- Miglioramento della qualità di ricezione.

- Nessun cambiamento delle abitudini: stesse frequenze, stesse condizioni di ascolto (fisso, mobile e portatile), negli stessi ambienti (al chiuso, in città, in fitte foreste etc...).

- Basso costo dei ricevitori e basso consumo di energia.

- Semplicità di sintonizzazione per frequenza, stazione o tipo di programma.

- Diversificazione del contenuto delle trasmissioni, grazie alle potenzialità del digitale.

- Possibilità di ricevere il segnale in aree geografiche attualmente irraggiungibili.

- Le emittenti potranno fornire informazioni ausiliari come titolo della canzone, cantante o nome della stazione.

Mentre per i produttori di apparati ricevitori, trasmettitori e semiconduttori:

- Aumentare la longevità della più vecchia tecnologia AM.

- Opportunità di definire nuove aree di interesse.

- Aumentare il mercato potenziale dei trasmettitori e ricevitori.

- Ottimizzare il ritorno dagli investimenti nella tecnologia duale per trasmissioni a bassa capacità.

- Possibilità di raggiungere un mercato di 2.5 miliardi di apparati ricevitori da rimpiazzare.

- Attraverso il consorzio DRM, possibilità di partecipare attivamente allo sviluppo dell'AM digitale.

### Ed infine per le emittenti in AM digitale:

- Possibilità di usare gli apparati già esistenti.

- Possibilità di usare, in maniera più efficiente, l'attuale pianificazione frequenziale.

- Controllo dell'area di copertura.

- Opportunità di aggiungere informazioni: dati, testo e altri servizi.

- Possibilità di aumentare il numero degli ascoltatori visto l'ampliamento dei servizi offerti.

- Come parte del consorzio DRM, attiva partecipazione nella fase di sviluppo dell'AM digitale.

## 2.2.1 Allocazione delle frequenze in banda AM

L'allocazione delle frequenze per il broadcasting sono precisate nell'International Radio Regulations, e modificate nel tempo in base alle necessità dalla World Radio Conferences. Nonostante ciò esistono alcune differenze spostandosi da una parte all'altra del mondo.

In banda LF ogni canale ha una larghezza di banda di 9 kHz e la frequenza centrale di tale banda può essere allocata tra 148.5 e 283.5 kHz.

In banda MF ogni canale ha una larghezza di banda si 9 kHz e la frequenza centrale di tale banda può essere allocata tra 526.5 e 1606.5 kHz.

In America la banda LF non è utilizzata, mentre in banda MF la larghezza dei singoli canali è di 10 kHz (tra 525 e 1705 kHz).

La banda HF può essere diversa da nazione a nazione, si può avere allocazione di banda per la radiofonia tra 2.3 e 27 MHz, con i singoli canali larghi 5 kHz, ma con un assegnazione nominale canale per di 10 kHz nominali. Mentre in alcune zone tropicali la parte bassa della banda HF è dedicata al broadcasting nazionale, mentre la restante resta libera per quello internazionale.

## 2.2.2 Propagazione delle ground-wave e delle sky-wave

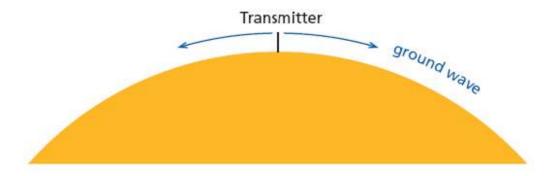

Una ground-wave è un'onda elettromagnetica che abbraccia la superficie curva della terra (come visibile in figura). La conducibilità e la costante dielettrica della terra influenzano la propagazione delle onde elettromagnetiche. Dette anche surface-wave, trovano la loro migliore propagazione sulla superficie dei mari (acqua salata), o comunque su superfici umide, piuttosto che su aree secche (come la sabbia dei deserti). Si utilizza la polarizzazione verticale in quanto quella orizzontale è fortemente attenuata.

Figura 12: Propagazione delle ground-wave

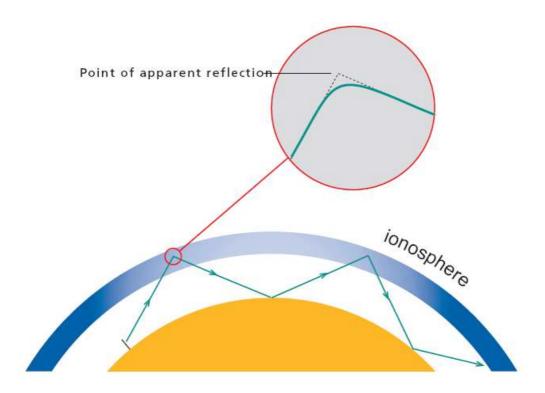

La propagazione delle sky-wave è possibile grazie alla ionosfera, che contiene uno strato di particelle cariche, ionizzate dai raggi solari, le quali interagiscono con le onde elettromagnetiche. Le onde incidenti sulla ionosfera possono essere assorbite o riflesse in funzione del grado di ionizzazione, della densità del gas e della frequenza. Il livello più basso della ionosfera (livello D) assorbe, specialmente nelle ore diurne, le onde in banda MF, ma i livelli sovrastanti (specie i livelli E ed F) riflettono le onde em così tanto da farle ritornare a terra. Quindi è come se l'onda avesse viaggiato da punto a punto sulla terra in linea retta, mentre in realtà questa è stata riflessa, quindi ha compiuto un percorso molto più lungo. Il segnale, una volta tornato a terra, se riflesso ancora dalla terra può tornare sulla ionosfera ed essere riflesso a terra nuovamente. Questo può portare il segnale a distanze notevoli, tale fenomeno è detto *multiple hops* (visibile in figura).

Figura 13: Propagazione delle sky-wave

Se la frequenza è troppo alta, le onde non sono sufficientemente riflesse per poter tornare a terra. Esiste una frequenza critica sopra la quale il fenomeno della riflessione non è efficace, la quale va decrescendo all'aumentare dell'angolo di incidenza (decresce se le onde arrivano più verticali).

Per il broadcasting internazionale le antenne trasmittenti sono studiate per favorire un'appropriata elevazione delle onde radio, in modo che la copertura desiderata venga realizzata mediante una o più riflessioni sulla ionosfera.

Esiste anche un altro metodo per coprire grandi aree mediante riflessione, consiste nel trasmettere le onde radio quasi verticalmente, le quali sono poi riflesse dalla ionosfera in una vasta area estesa intorno al trasmettitore. Questo significa che è possibile realizzare coperture anche in caso in cui le groundwave non riescono a garantirla. Questo tipo di trasmissione *near-vertical incidence skywave* (NVIS) richiede che le frequenza di trasmissione sia inferiore a quella critica, infatti nelle zone tropicali la parte bassa della banda HF è mantenuta libera a questo scopo. Un problema di questo metodo è che se le perdite sulla ionosfera sono molto basse, nelle zone vicine al trasmettitore si

verificano forti disturbi dovuti al multipath, in quanto vengono ricevuti i segnali relativi alle ground-wave, alla prima riflessione sulla ionosfera, alla seconda, alla terza e così via.

Figura 14: Propagazione NVIS

### 2.3 Standard ETSI ES 201 980 v2.2.1

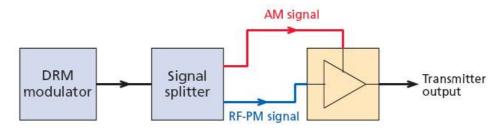

Come detto, le specifiche del sistema DRM sono illustrate nello standard ETSI ES 201 980 v2.2.1, pubblicato nell'agosto 2005 dopo alcune modifiche apportate alle versioni precedenti. La descrizione seguirà fedelmente il flusso dalla sorgente audio, fino a giungere al segnale DRM, ovvero il flusso di un trasmettitore DRM (DRM encoder). Nella figura sottostante è rappresentato lo schema di principio del trasmettitore, del quale verranno analizzate, sezione per sezione, tutte le principali caratteristiche.

Figura 15: Schema a blocchi di un trasmettitore DRM

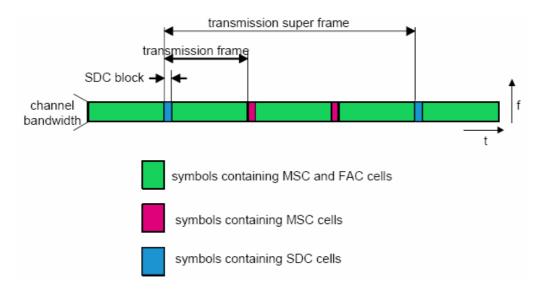

Va specificato che tipicamente nelle bande di interesse del DRM i canali hanno una banda nominale di 9/10 kHz. Il sistema DRM è in grado di supportare anche larghezze di banda doppie, ovvero 18/20 kHz, oppure metà di tali larghezze di banda, ovvero 4.5/5 kHz. Per ciascuno di questi canali va detto che la capacità è dipende da che livello di immunità da disturbi (rumore, multipath, doppler) si desidera conferire al segnale. Questo viene realizzato attraverso la scelta di opportune costellazioni e modalità OFDM. Tipicamente con un canale di 9/10 kHz (larghezza di banda più diffusa) si riesce a trasportare un data rate di 20-24 Kbit/s, mentre con un canale di ottengono 18/20 kHz si arriva fino a 72 Kbit/s. Questo è molto importante in quanto ne va tenuto conto nella fase di compressione e codifica del payload. Nello schema di principio va tenuto conto che non vi è differenza tra le diverse classi di informazione (audio, data, etc.), e in un singolo canale possono essere trasmessi fino a quattro stream audio o dati, quindi è necessario ripartire i Kbit/s disponibili nel miglior modo possibile per tutti i servizi che si intendono inserire all'interno di un singolo canale (è possibile anche inserire un numero minore di quattro stream in un singolo canale).

## 2.3.1 La codifica di sorgente – MPEG-4

Lo stream audio, derivante dal campionamento in real time di un segnale audio proveniente da qualsiasi tipo dei fonte, (tipicamente 44.100 kHz @ 16 bit) presenta un bit rate di circa 700 Kbit/s, quindi di gran lunga maggiore alla capacità dei canali, quindi è necessario comprimere tale segnale. Per offrire la migliore qualità audio ed il bit rate desiderato sono disponibili diversi schemi di compressione audio:

a) Un sottoinsieme dell'MPEG-4 AAC (Advanced Audio Coding), che permette di ottenere qualsiasi valore di bit rate in uscita, sia mono che stereo. È utilizzato un Byte-Alignment di 400ms (audio super frame) che porta ad avere circa 20 kbit/s. Le frequenze di campionamento consentite sono di 12 e 24 kHz. La Transform Length è 960, per assicurare che un audio frame corrisponda a 80ms o a 40ms. Questo è

necessario per assicurare che nelle modalità AAC e CELP l'audio super frame sia costituito da un numero intero di audio frames. Per quel che riguarda la resistenza agli errori è utilizzato un subset dei tools dello standard MPEG-4, particolarmente efficiente in canali inclini disturbi. Cinque audio frame (@ 12 kHz sampling rate) o dieci (@ 24 kHz sampling rate) compongono un audio super frame, che corrisponde sempre a 400ms; lo scambio di bit tra audio frame è possibile solamente per frame all'interno dello stesso superframe, il quale è poi posto in un frame logico, in modo tale che non è necessaria una sincronizzazione aggiuntiva per l'audio coding (è sufficiente la sincronizzazione generale del sistema). Nei casi in cui fosse presenta un alto BER (Bit Error Rate) è sempre possibile applicare una protezione da errore di tipo UEP (Unequal Error Protection) al fine di ottenere una minore degradazione della qualità audio; questa operazione è realizzata nella sezione di multiplex.

- Prediction), ottimo per la compressioni di un segnale audio mono contenente solo parlato, resistente agli errori, utile quando si dispone solo di un basso bit rate (tra 4 e 10 Kbit/s, tipicamente 8 Kbit/s) e specialmente quando è richiesto un alto livello di robustezza del segnale. Con questo tipo di codifica è possibile inserire fino a tre stream audio contemporaneamente in un singolo canale, oppure è possibile aggiungere un servizio contenente solo parlato ad un servizio audio; nella trasmissione Simulcast, dove coesistono canali analogici e digitali. Spesso sono disponibili canali con capacità non superiore a 8 Kbit/s quindi la codifica AAC non è applicabile e bisogna ricorrere alla CELP. È possibile utilizzare una data rate di 8 Kbit/s anche in canali da 20 Kbit/s per garantire un'ottima robustezza del segnale. Le frequenze di campionamento utilizzate sono 8 e 16 kHz, ed anche in questo caso un numero intero di frame audio vanno a comporre l'audio super frame.

- c) Un sottoinsieme dell'MPEG-4 HVXC (Harmonic Vector eXcitation Coding) adatto per un parlato mono a bit rate estremamente basso (tipicamente 2 kbit/s). Questo tipo di compressione audio apre al DRM

nuovi scenari, infatti è possibile aggiungere servizi audio (parlati) ausiliari ad altri tipi di streaming, si possono realizzare trasmissioni multi lingua, è possibile registrare su 4.5 Mbytes di memoria flash fino a 4.5 ore di programma, la velocità ed il pitch di riproduzione sono definibile dall'utente. Inoltre il regnale presenta un elevatissima resistenza agli errori con o senza schemi di modulazione gerarchica, garantita anche dalla presenza di un codice CRC (Cyclic Redundant Code). La frequenza di campionamento è 8 kHz, e si ottengono bit rate compresi tra i 2.0 e i 4.0 Kbit/s. Anche in questo caso un audio super frame è composto da un numero intero, venti, di audio frames.

| Codec | Content      | Possible<br>bit rates | Authors' recommended bit rates |

|-------|--------------|-----------------------|--------------------------------|

| HVXC  | Speech       | 2-4 kbit/s            | 2-4 kbit/s                     |

| CELP  | Speech       | 4-24 kbit/s           | 8-16 kbit/s                    |

| AAC   | Speech/Music | 8-20 kbit/s           | 12-20 kbit/s                   |

Figura 16: MPEG-4 bit rates

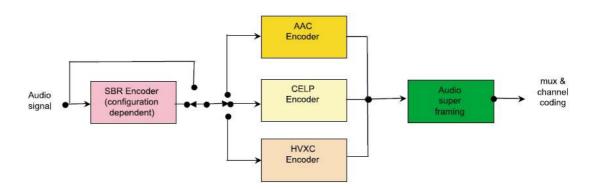

Figura 17: DRM source encoder